©2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

# MULTICARRIER MODULATED MULTI LEVEL INVERTER BASED DVR AND DSTATCOM FOR MITIGATING SWELL

G. Annapurna<sup>1</sup> and G.Tulasiramdas<sup>2</sup>

<sup>1</sup>G. Narayanamma Institute of Technology and Science, Hyderabad, India <sup>2</sup>Jawaharlal Nehru Technological University Hyderabad, Hyderabad, India E-Mail: gootyanu@gmail.com

## **ABSTRACT**

The most commonly occurring power quality issue such as voltage swell may cause mal- operation and loss of production. This paper presents voltage swell reduction technique using multi-level inverter based DVR and DSTATCOM employing CBSVPWM algorithm. SVPWM generates fewer harmonics when compared to SPWM. However, as the number of levels in the inverter output voltage increases, the control complexity also increases. To reduce the complexity involved in conventional SVPWM, a novel modulation scheme, CBSVPWM is presented in this paper. The proposed 3 level and 5 level neutral point clamped DVR and DSTATCOM are simulated using multicarrier based SVPWM technique for generating pulses to the inverter. Simulations carried out using MATLAB/SIMULINK prove that the proposed control algorithm is able to compensate any type of voltage swell and also compensation is perfect with negligible THD.

Keywords: dynamic voltage restorer, distribution static compensator, space vector modulation, neutral point clamped inverter.

#### INTRODUCTION

The use of sophisticated electrical and electronics equipment such as computers, variable speed drives etc. demand high quality power supply. Power quality issues such as swells, sags and harmonics affect the performance of the sensitive loads. New technologies have introduced flexible controllers to mitigate the power quality problems. A voltage swell is an increase to the value between 1.1 to 1.8 PU in RMS value at power frequency for durations less than 1 minute.

These unwanted voltage swells can be reduced by connecting custom power devices either in series or shunt to the load. DVR and D-STATCOM are two such devices to mitigate swells. DVR is a series device to inject dynamically controlled voltage in series with the system bus voltage and the D-STATCOM is a shunt connected device used to inject a dynamically controlled current in shunt with bus voltage through injection transformers.

In recent years, multilevel inverters have gained importance in medium voltage, high power applications because of their better performance compared to two-level inverters, such as reduced harmonics in output voltage and current, lower dv/dt and lower switching losses. Neutral Point Clamped Inverters are most widely used in distribution system applications because of their own advantages [1].

This paper presents an effective voltage compensation scheme by DVR and DSTATCOM employing CBSVPWM. In conventional SVPWM, sector identification, switching-vector determination and switching-time calculation are time consuming and quite complicated. As the number of inverter output levels increases, the control complexity also increases. To decrease the complexity in the conventional control algorithm, a novel modulation scheme known as carrier based SVPWM is introduced. In this proposed algorithm,

there is no need to use look up table for sector identification and can be easily extended to m- level [2-4].

The present paper employs the most popular Level Shifted Phase Disposition multicarrier modulation method for generating the PWM pattern in which (m-1) carrier signals are compared with the modulating signal to generate 'm' levels in the inverter output voltage [5].

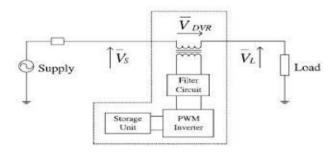

## DYNAMIC VOLTAGE RESTORER

DVR is a series connected custom power device to protect sensitive loads from voltage disturbances such as swells, sags and harmonics etc. DVR injects controllable voltage through an injection transformer in series with the bus voltage such that desired voltage magnitude can be maintained at the load as shown in Figure-1. When supply voltage  $V_s$  changes, the DVR injects a voltage  $V_{DVR}$  so as to maintain the load voltage at desirable level. DVR is simply a VSC that produces an ac output voltage and injects in series with supply voltage through a transformer [6-8].

Figure-1. Schematic representation of the DVR.

The main objective of the control circuit is to maintain constant voltage at the point of common coupling

©2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

## www.arpnjournals.com

at which a sensitive load is connected, under system disturbances. In this scheme, only rms value of terminal voltage is measured and reactive power measurement is not required [9-10].

The error signal obtained after comparing the reference voltage with measured terminal voltage is used to generate modulating signals in case of SPWM and SVPWM techniques.

This modulating signal is then compared with carrier (triangular) signals to generate the switching signals for the converter switches in both modulation techniques. The SPWM technique is very simple and easy to implement. But, in this paper, it is aimed to prove that Space Vector Pulse Width Modulation is efficient and offers good response.

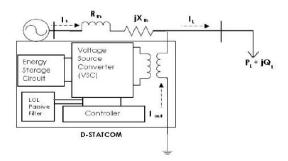

## DISTRIBUTION STATIC COMPENSATOR

The D-STATCOM is a VSC which injects dynamically controlled current in shunt with bus voltage through coupling transformer. This shunt injected current corrects the voltage swells by adjusting the voltage drop across the system impedance. The injected current magnitude can be controlled by adjusting the output of the converter. The DSTATCOM consisting of a VSC, a DC energy storage device and a coupling transformer connected in shunt with the AC system is shown in Figure-2[11-13].

The shunt connected VSC has a multifunctional topology and can be used for the following different purposes:

- a) Voltage regulation and compensation of reactive power

- b) Correction of power factor and

- c) Elimination of current harmonics.

In this present work, such device is employed for voltage regulation.

Figure-2. Schematic representation of the D-STATCOM.

From the schematic diagram, it is clear that the value of  $I_{\text{out}}$  can be controlled by adjusting the output voltage of the converter.

The shunt injected current  $I_{\text{out}}$  can be written as,

$$I_{out} = I_L - I_S = I_L - (V_{TH} - V_L / Z_{TH})$$

(1)

Where,  $I_I = load$  current,

$I_S$  = source current,  $V_{TH}$  = thevenin voltage,

$V_L$  = load voltage and  $Z_{TH}$  = thevenin impedance

$$I_{\text{out}} \angle \gamma = I_{\text{L}} \angle - \theta - \frac{V_{TH}}{Z_{TH}} \angle (\delta - \beta) + \frac{V_L}{Z_{TH}} \angle (-\beta)$$

(2)

From the above equation, it is clear that  $I_{out}$  will correct the voltage sags or swells by adjusting the voltage drop or rise across the system impedance.

Here also, the control system measures only the rms terminal voltage and reactive power measurement is not required and same control scheme is applicable for both DVR and DSTATCOM.

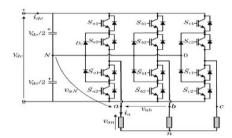

# MULTILEVEL NEUTRAL POINT CLAMPED INVERTER

Figure-3 shows three level neutral point clamped (NPC) topology. Each leg consists of four switches and two clamping diodes. The DC supply is composed of two capacitors in series and the voltage is split into three levels (+V $_{\text{dc/2}}$ , 0, -V $_{\text{dc/2}}$ ) thereby reducing the stress on the switches.

Figure-3. Three-level NPC inverter topology.

The phase A output voltage Vao can have three different levels: +Vdc/2, 0, -Vdc/2. For voltage level+Vdc/2,Sa1 and Sa2 are turned ON, for 0 level Sa2 and Sa1' are turned ON and for voltage level -Vdc/2 Sa1' and Sa2' are turned ON. These states can be defined as 2, 1, and 0 respectively.

**Table-1.** Switching variables of three level inverter.

| States<br>mode     | $S_{a1}$ | $S_{a2}$ | Sa1' | Sa2' | $S_a$ |

|--------------------|----------|----------|------|------|-------|

| $+V_{dc/2}$        | ON       | ON       | OFF  | OFF  | 2     |

| 0                  | OFF      | ON       | ON   | OFF  | 1     |

| -V <sub>dc/2</sub> | OFF      | OFF      | ON   | ON   | 0     |

A five level NPC inverter consists of eight switching devices per phase and four clamping diodes. The DC supply consists of four capacitors in series and the

©2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

## www.arpnjournals.com

voltage is split into five levels (  $+V_{dc/2}$ ,  $+V_{dc/4}$ , 0,  $-V_{dc/4}$ ,  $-V_{dc/2}$ ).

#### MODULATION STRATEGY

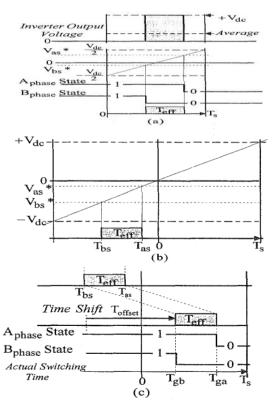

#### Carrier based SVPWM scheme

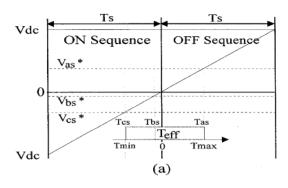

As shown in Figure-4(a), during one sampling interval, when the switching state becomes '0' from '1' for each phase at different time, an effective voltage will be applied to the load. Ts is the sampling time,  $T_{\rm eff}$ , is the difference between two switching times  $T_{\rm as}$  and  $T_{\rm bs}$  is called the 'effective time'. If the value of  $T_{\rm eff}$  is negative, then a negative voltage is applied to the load, i.e.  $T_{\rm bs}$  is greater than  $T_{\rm as}$ .

As the time must be positive, transition of the switching state must take place during a consecutive sampling interval. The effective time determines the inverter output voltage and so the theory of time can be extended to negative region as shown in Figure-4(b).

With the introduction of imaginary time value, the relation between time and voltage for the operation of one leg of inverter can be deduced as follows:

$T_{as} = \frac{Ts}{Vdc} V_{as}$ , where  $V_{as}$  is the phase A voltage on the load side.

(a) Relationship between the effective time and the output voltage. (b) Extended concept for effective time. (c) Actual gating time generation.

Figure-4. PWM implementations.

The same principle can be applied for the remaining phases also. These times  $T_{as,}T_{bs}$  and  $T_{cs}$  are called 'imaginary switching times' and from these imaginary switching times, the effective time can be obtained as follows:

$$T_{eff} = T_{as} - T_{bs} = \frac{Ts}{Vdc} (V_{as} - V_{bs})$$

(3)

While generating the actual gating signals, we have one degree of freedom using which the effective time can be relocated anywhere within the sampling interval. In order to generate the actual gating pulses for each inverter leg, time shifting operation is applied to the imaginary switching times as follows:

$$T_{ga} = T_{as} + T_{offset},$$

$$T_{gb} = T_{bs} + T_{offset}$$

$$T_{gc} = T_{cs} + T_{offset}.$$

$$(4)$$

With this principle, inverter operation can be performed accurately using a simple equation and the same can be easily extended to 3 phase scheme also. The imaginary times are defined as follows:

$$T_{as} = \frac{Ts}{Vdc} V_{as}^*, T_{bs} = \frac{Ts}{Vdc} V_{bs}^* \text{ and } T_{cs} = \frac{Ts}{Vdc} V_{cs}^*$$

(5)

In Space vector PWM method, the constant reference voltage vector v \* can be represented by means of the two nearest active vectors as follows.

$$V^* = (T_1.V_n + T_2.V_{n+1}) / T_s$$

(6)

The applying times  $T_1$  and  $T_2$  are not the actual gating times, but are the time durations in which active vectors are applied. These can be deduced as follows.

©2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

## www.arpnjournals.com

(a) Relationship between the effective time and the output voltage.(b) CBSVPWM gating generation.

**Figure-5.** PWM implementations by the proposed PWM method (in case of Sector 1)

$$T_{1} = \frac{\sqrt{3.Ts}}{Vdc} \underbrace{\begin{bmatrix} \sqrt{3} \\ 2 \end{bmatrix} V_{d}^{s} - \frac{1}{2} V_{q}^{s} \\ = \frac{Ts}{Vdc} \underbrace{\begin{bmatrix} V_{d}^{s} + (\frac{1}{2} V_{q}^{s} - \frac{\sqrt{3}}{2} V_{d}^{s} \\ \end{bmatrix}}_{2} = T_{as} - T_{bs}$$

$$T_{2} = \frac{\sqrt{3.Ts}}{Vdc} \underbrace{\begin{bmatrix} V_{q}^{s} \end{bmatrix}}_{2} = T_{bs} - T_{cs}$$

$$(7)$$

From the above, it is evident that the applying times  $T_1$  and  $T_2$  are nothing but the effective times. The zero time is to be symmetrically distributed in one sampling period as shown in Figure-5(b), such that the whole modulation task of SVPWM is completed. With the help of a sorting algorithm,  $T_{\text{max}}$  and  $T_{\text{min}}$  will relocate the effective time at the centre of the sampling period. Thus, the actual gating signals for inverter phase can be obtained using the time shifting operation as given below.

$$T_{ga} = T_{as} + T_{offset}, T_{gb} = T_{bs} + T_{offset},$$

$$T_{gc} = T_{cs} + T_{offset},$$

(8)

The time shifting value is

$$T_{offset} = \frac{1}{2} T_{0} - T_{min} Where, T_{eff} = T_{max} - T_{min} .$$

(9)

$$T_{max} = \max(T_{as}T_{bs}T_{cs)}, T_{min} = \min(T_{as}T_{bs}T_{cs)}$$

$$T_0 = T_s - T_{eff}$$

(10)

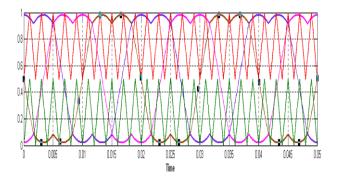

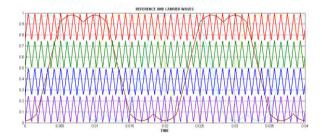

Carrier based SVPWM scheme is adopted for 3 level and 5 level Neutral Point Clamped inverter based DVR and DSTATCOM for swell reduction. In this multilevel carrier based scheme, to generate 'm' level output voltage, (m-1) carrier signals are required. Therefore, in this work, the modulating wave is compared with two level shifted carrier signals for 3 level inverter and four carrier signals for 5 level inverter.

**Figure-6.** Level shifted multi carrier waves and Space Vector modulating wave for three level inverter.

**Figure-7.** Level shifted multi carrier waves and Space Vector modulating wave for five level inverter.

## SIMULATION RESULTS

## Simulation results of unbalanced swell

In order to evaluate the performance of DVR and DSTATCOM for unbalanced and balanced compensation in voltage, initially, a voltage swell is deliberately created in two phases only. However, both DVR and DSTATCOM can handle balanced and unbalanced swells very effectively and the same is presented under heading of "simulation results for both balanced and unbalanced swells".

## www.arpnjournals.com

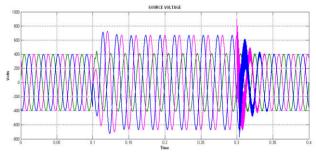

## Simulation results of three level DVR

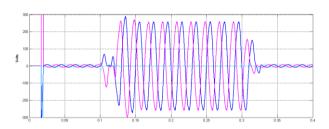

Figure-8. Source voltage.

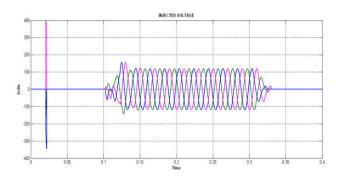

Figure-9. Injected voltage.

Figure-8.Shows swell of 270V (i.e. a voltage of 670V during swell) in two phases and Figure-9 indicates the injection of 99.1% in phase opposition.

## Simulation results of five level DVR

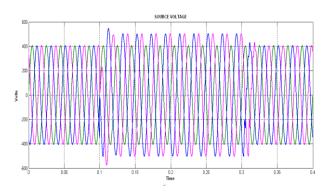

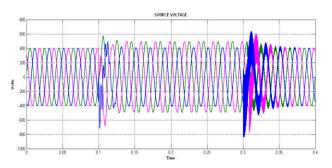

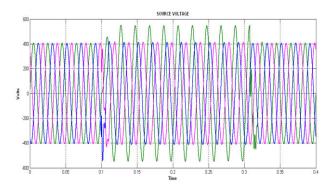

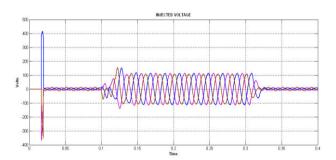

Figure-10. Source voltage.

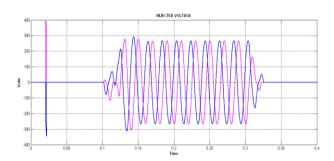

Figure-11. Injected voltage.

Figure-10 shows swell of 100V in two phases (i.e. total voltage during swell is 500V) and Figure-11 indicates injection of almost 100% in the two phases.

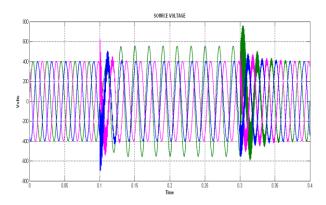

## Simulation results of three level DSTATCOM

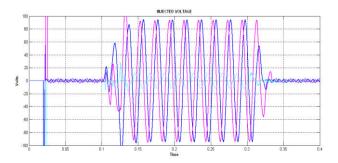

Figure-12. Source voltage.

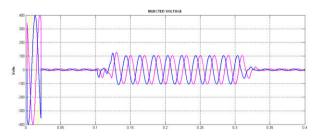

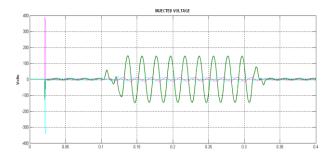

Figure-13. Injected voltage.

Figure-12.Shows swell of 270V in two phases and Figure-13 indicates voltage injection of 96.2%.

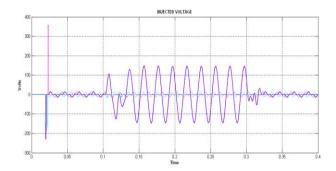

## Simulation results of five level DSTATCOM

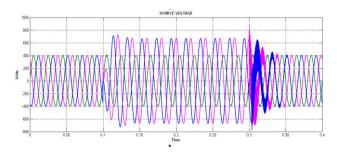

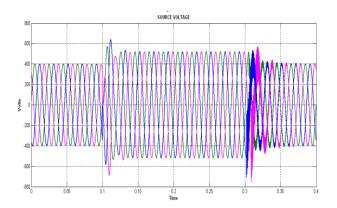

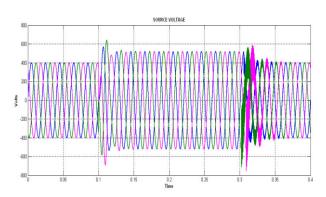

**Figure-14.** Source voltage.

Figure-15. Injected voltage.

©2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

## www.arpnjournals.com

Figure-14 shows swell of 100V in two phases and Figure-15 indicates 97% of voltage injection in the two phases.

## Simulation results for bothbalanced andunbalanced swells

## Simulation results of 3 level DVR

Figure-16. Source voltage.

Figure-17. Injected voltage.

Figure-16.Shows swell in three phases and Figure-17 indicates the injected voltage in all the three phases.

## Simulation results of 5level DVR

Figure-18. Source voltage.

Figure-19. Injected voltage.

Figure-18 shows swell in one phase and Figure-19 shows the injected voltage in one phase in opposition.

## Simulation results of 3 level DSTATCOM

Figure-20. Source voltage.

Figure-21. Injected voltage.

Figure-20 shows swell in all the three phases and Figure-21 indicates the injected voltage.

©2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

## www.arpnjournals.com

#### Simulation results of 5 level DSTATCOM

Figure-22. Source voltage.

Figure-23. Injected voltage.

Figure-22 shows swell in one phase and Figure-23 indicates the injected voltage in phase opposition.

The THD in the load voltage after compensation of swell is measured and tabulated below.

**Table-2.** Comparison of voltage injection and THD in the load voltage.

| Inverter | DV                  | R        | DSTATCOM            |          |  |

|----------|---------------------|----------|---------------------|----------|--|

| levels   | % voltage injection | %TH<br>D | % voltage injection | %TH<br>D |  |

| 3        | 99.1                | 2.52     | 96.2                | 4.29     |  |

| 5        | 100                 | 1.48     | 97                  | 2.93     |  |

#### CONCLUSIONS

The three level and five level inverter based DVR and DSTATCOM are simulated using carrier based SVPWM technique for compensation of swell. For the purpose of evaluation of the performance of both DVR and DSTATCOM for balanced and unbalanced voltage compensation, initially, voltage swell is created deliberately in two phases only. Later, simulations were carried out for both balanced (three phase swell) and unbalanced (swell in single phase) conditions also. From the simulation results, it is clear that DVR and DSTATCOM can compensate both balanced and

unbalanced swells effectively. But, DVR is capable of regulating the voltage more effectively compared to DSTATCOM. It is also observed that the total harmonic distortion in the load voltage is less in case of DVR compared to DSTATCOM and also as the inverter output levels increase; the THD in the load voltage reduces. However, there is not much difference in the injected voltage of 3 level and 5 level inverters. The above technique can be extended for higher levels for further reduction in the THD content.

#### REFERENCES

- [1] José Rodríguez, Jih-Sheng Lai, Fang ZhengPeng. Multilevel Inverters: A Survey of Topologies, Controls, and Applications. IEEE Transactions on Industrial Electronics. 49(4): 724-748.

- [2] Dae-Woong Chung, Joojn-Sheok Kim and Seung- Ki Sul. Unified voltage modulation technique for real time three phase power conversion. IEEE transactions on Industry Applications. 34(2): 374-380.

- [3] S.Aswak Hussain, K.Chandra Sekhar and T.Bramhananda Reddy. 2011. Generalized PWM Algorithm for three phase n-level voltage source inverter fed AC drives. International Journal of Advances in Science and Technology. 2(6).

- [4] G.Sree Lakshmi, S.Kamashaiah and G.Tulasiramdas. 2014. Simulation of DTC-CBSVPWM fed SPMSM drive with five- level diode clamped inverter. International Journal of Computer Applications. 87(1).

- [5] R. Balamurugan, S. P. Natarajan, R. Bensraj. 2012.Investigations on Three Phase Five Level Diode Clamped Multilevel Inverter.International Journal of Modern Engineering Research. 2(3): 1273-1279.

- [6] Rosli Omar, NasrudinAbd Rahim. Modelingand Simulation for Voltage Sags/Swells Mitigation Using Dynamic Voltage Restorer (DVR). Australasian Universities Power Engineering Conference (AUPEC'08).

- [7] R. Omar, M. Sulaiman, N. Abd Rahim. 2010. Voltage Sag Mitigation Using Dynamic Voltage Restorer Based On Space Vector PWM (SVPWM). Iranian Journal of Electrical and Computer Engineering. 9(2)Summer-Falls.

- [8] P.Usha Rani, S.Rama Reddy. 2011. Dynamic Voltage Restorer Using Space Vector PWM Control

©2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

## www.arpnjournals.com

Algorithm. European Journal of Scientific Research. 56(4): 462-470.

- [9] S.V Ravi Kumar and S. Siva Nagaraju. 2007. Simulation of D-STATCOM and DVR in Power Systems. ARPN Journal of Engineering and Applied Sciences. 2(3).

- [10] C. Sharmeela, G.Uma, M.R. Mohan and K. Karthikeyan. Multilevel distribution STATCOM and DVR for voltage sag and swell reduction. IIT, Madras Dec' 27-30.

- [11] P. Ramesh, C. Surya Chandra Reddy, D. Prasad, D. Prameela, A.Anusha. 2012. Mitigation of faults in the distribution system by distributed static compensator (DSTATCOM). International Journal of Modern Engineering Research. 2(2): 506-511.

- [12] Noramin Ismail, Wan Norainin Wan Abdullah. 2010. Enhancement of Power Quality in Distribution System Using D-STATCOM. The 4<sup>th</sup> International Power Engineering and Optimization Conference (PEOCO2010), ShahAlam, Selangor, Malaysia.

- [13] SaiKiran Kumar, Sivakoti, Y.Naveen Kumar, D.Archana. Power Quality Improvement Distribution **D-STATCOM** System Using in Transmission Lines. International Journal Engineering Research and Applications. 1(3): 748-752.