© 2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

# RF ENERGY HARVESTING WITH EFFICIENT MATCHING TECHNIQUE FOR LOW POWER LEVEL APPLICATION

Ismahayati Adam<sup>1</sup>, Mohd Fareq Abd Malek<sup>1</sup>, Mohd Najib Mohd Yasin<sup>2</sup> and Hasliza A. Rahim<sup>1</sup> School of Computer and Communication Engineering, Universiti Malaysia Perlis (UniMAP), Malaysia <sup>2</sup>School of Microelectronic Engineering, Universiti Malaysia Perlis (UniMAP), Malaysia E-Mail: <a href="mailto:ismahayati@unimap.edu.my">ismahayati@unimap.edu.my</a>

## ABSTRACT

Development of energy harvesting and wireless power transfer have emerged batteryless and non-contact energy transfer. For optimum power transfer between antenna and the rectifier circuit, impedance of the antenna and rectifier should be match. This paper describes the design and implementation of the 7-stage multiplier in energy harvesting. A Modified dickson configuration is chosen, consists of two HSMS 2850 Schottky diodes and two capacitors for each stage. The aim of this paper is to analyze the performance of the designed rectifier together with matching network. Simulation results show an improvement for the multiplier circuit with a matching network compare to the multiplier alone. Maximum of 60% improvement in rectified output has been achieved at low input power.

**Keywords:** energy harvesting, wireless power transfer, dickson multiplier, matching network.

#### INTRODUCTION

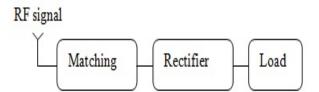

Radio Frequency (RF) energy harvesting technology is not new, it has been studied years before by many researchers (Sogorb *et al.* 2008; Muramatsu & Koizumi, 2010; Jabbar *et al.* 2010; Kim, 2011; Matiko *et al.* 2014). Due to unpredictability of source like wind, light, vibration, piezoelectric and other sources, RF became a more popular source in harvesting energy for its availability and easy scavenging system. RF energy can be harvested either from ambient or from dedicated source. A device designed to collect the electromagnetic energy in the free space and transform into direct current (DC) is called rectenna. Typical RF energy harvester or rectenna is shown in Figure-1 where it is basically a combination of rectifier and antenna.

Figure-1. General block diagram of rectenna.

As depicted in Figure-1, a matching network is applied between the antenna and the rectifier circuit. The existence of matching circuit is crucial as it can improve the RF to DC efficiency of the rectenna. A good matching network will allow a maximum power transfer between the antenna and the rectifier circuit.

Availability of RF energy in the surrounding or areas close to transmission towers provides an an opportunity to harvest the unused energy, particularly in GSM and WLAN band. Despite this band, exploring the possibility in harvesting an energy form RF broadcasting wave is riveting research (Sogorb *et al.* 2008; Mikeka *et al.* 2011; Keyrouz *et al.*2012).

Harvesting RF ambient power from Digital Television (DTV) signals was first investigated by Intel where 60uW of energy was harvested at a distance of 4 km from the broadcasting TV station (Keyrouz *et al.* 2012). RF energy harvesting in the Digital TV (DTV) band is presented in (Mikeka *et al.* 2011), where the rectifying antenna, given a single tone excitation at 550 MHz, has a measured conversion efficiency of 0.4% for -40 dBm input and 18.2% for -20 dBm input, respectively. Power of +3 dBm and -44 dBm are measured from Tokyo tower TV broadcasting at 400 m and 4 km correspondingly.

In this paper, the possibility of harvesting energy from commercial RF broadcasting stations is investigated. Matching technique has been focus in this research as an alternative in increasing the efficiency. The designed circuit is targeted to harvesting energy from ultra-high frequency (UHF) channel 29 with centre frequency of 540 MHz. The designed multiplier in this paper is successfully covered the channel bandwidth from 535.5 MHz to 541.5 MHz.

## **DESIGN**

# Rectifier design

The rectifier presented is this paper is based on 7-stage Dickson multiplier with Schottky diode as stated in Figure-2. Each stage is consisting of two diodes and two capacitors. Typically, output from a single stage rectifier is very low since the captured energy is low, thus by cascading the circuit, a higher DC voltage can be obtained from an AC input. The cascaded circuit is called Dickson multiplier

This circuit is a Dickson multiplier that has been previously modified by Karthaus and Fischer in 2003, where it has fewer requirements than original Dickson topology. The circuit do not need of clock pulses to operate, so did the numbers of coupling and stray capacitors were reduced.

© 2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

### www.arpnjournals.com

**Figure-2.** Dickson n-stage rectifier configuration (Karthaus & Fischer, 2003).

The rectify elements in the circuit mainly determines the RF to DC conversion efficiency and Schottky diodes appeared to be a good candidate as they widely used (Zhang et al. 2013; Keyrouz et al. 2012; Jabbar et al. 2010; Devi et al. 2011). Due to high operating frequency and low input power, diodes should have a very fast switching time and the lowest possible turn on voltage (Merz. et al. 2014). Schottky diodes offer great advantages in terms of speed because it does not rely on holes or electrons recombining when they enter the opposite type of region as in the case of a conventional diode. Moreover, the diode has a much higher current density than an ordinary PN junction, means that low forward voltage drop, thus less energy is wasted as heat, making them the most efficient choice for applications sensitive to efficiency. Hence, HSMS2850 Schottky diodes were selected in this circuit as they have low turn on voltage and have been designed and optimized for use in small signal (for input power less than -20 dBm) applications at frequencies below 1.5 GHz (Avago Tech.). While, 4.7 nF capacitor is used in each stage capacitor.

The circuit has been simulated based on a low cost FR-4 board (with dielectric constant,  $\epsilon_r = 4.6$ , and substrate thickness, t = 1.6 mm). The circuit dimension is 90 mm x 78 mm. All the design and results are simulated in Advanced Design System (ADS) software.

#### Matching network

To increase the conversion efficiency, the designed circuit should resonate at the targeted frequency. A matching circuit is designed to match the impedance of the multiplier circuit to the standard 50  $\Omega$  antenna in order to allow maximum power transfer from the antenna to the circuit.

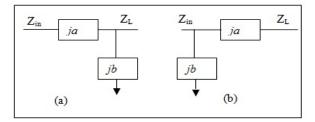

Figure-3. L matching configuration (a)  $Z_{in}$  less than  $Z_L$  (b)  $Z_{in}$  greater than  $Z_L$ .

To keep the losses in the circuit as minimum as possible, L matching network is applied as it has only two lumped elements in the matching circuit as shown in Figure x. Configuration in Figure-3 (a) is for input impedance ( $Z_{\rm in}$ ) lower than load impedance ( $Z_{\rm L}$ ) and Figure-3 (b) is for  $Z_{\rm in}$  greater than  $Z_{\rm L}$ . Element ja and jb in the circuit are reactive component, can be either inductor or capacitor. For a single frequency, any positive-real complex impedance can be matched to any other positive-real complex impedance using no more than two reactive component (Rhea R., 2006).

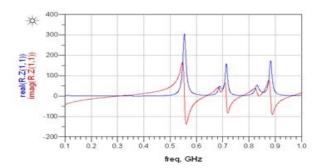

Figure-4. Impedance of the multiplier at 540 MHz.

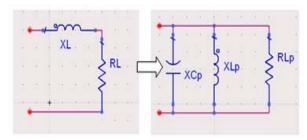

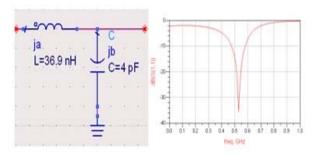

In the designed multiplier circuit, the input impedance at 540 MHz is equal to 57.7 + j 132.9  $\Omega$ , which is complex impedance and greater than 50  $\Omega$ . Thus, configuration in Figure-3 (a) is chosen. To simplify the calculation, the circuit needs to be transform to a resistive load only. So, the siries load impedance is converted to parallel, where it new value is 364  $\Omega$  for  $R_{Lp}$  and +j158  $\Omega$  for  $X_{Lp}$  and negative reactance,  $X_c$  is added parallel with  $X_{Lp}$  to eliminate the positive reactance as can be seen in Figure-5.

**Figure-5.** (a) Impdedance equivalent circuit, (b) parallel impedance transformation.

© 2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

### www.arpnjournals.com

$$a = R_{in} \left( \sqrt{\frac{R_{Lp}}{R_{in}} - 1} \right) \tag{1}$$

$$b = R_{Lp} \left( \sqrt{\frac{R_{Lp}}{R_{in}} - 1} \right)^{-1}$$

(2)

By applying both formula (1) and (2), the reactance of a and b is calculated as 125  $\Omega$  and 145  $\Omega$ . Then, the value of L and C is determined as 36.9 nH and 4 pF, taking into account the value of XCp. The reflection coefficient is found at 540 MHz with -38.8 dB deep exhibit bandwidth of 106 MHz. It is clear from the Figure 6 that the calculated matching element will match the impedance of multiplier and the 50  $\Omega$  antenna.

**Figure-6.** Proposed matching network (a) matching circuit, and (b) reflection coefficient of the matching circuit.

#### RESULTS AND DISCUSSION

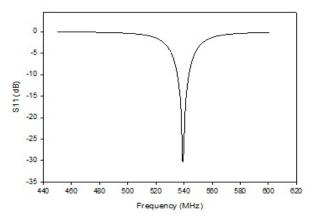

All the results discuss here are simulated by using Advanced Design System 2013 (ADS). The rectified output voltage is simulated across 100 pF parallel with 100  $k\Omega$  loads. As can be seen in Figure-7, a good match is achieved when the matching network is combined to the multiplier circuit, where 9 MHz bandwidth was obtained with -36.6 dB deep at 539 MHz.

**Figure-7.** Reflection coefficient of the multiplier with the matching network.

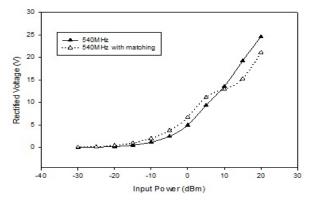

The rectified output voltage of the circuit is then measured to verify the circuit performance without and

with matching network. At the resonant frequency, which is 540 MHz, the result showed that there are improvements in the rectified output for an input power from -30 dBm to +5 dBm after the matching network is applied ahead of the circuit. 6.7 V is achieved at 0 dBm input power for circuit with matching, while 4.9 V for circuit without matching.

**Figure-8.** Rectified output voltage of the multiplier circuit at 540 MHz.

Data in Table-1 illustrated the rectified output voltage at 535 MHz and 545 MHz for multiplier with and without matching network. The ouput voltage follow the same trend as where it gives higher rectified voltage when the matching network is applied for low input power as compare to circuit without matching. Based on these results, it can be concluded that the circuit with matching network is optimized for lower input power.

**Table-1.** Simulated results with and without matching network for the proposed multiplier.

| Pin<br>(dBm) | 535 MHz (Volt) |       | 545 MHz (Volt) |       |

|--------------|----------------|-------|----------------|-------|

|              | No<br>Match    | Match | No<br>Match    | Match |

| -30          | 0.021          | 0.051 | 0.025          | 0.049 |

| -25          | 0.062          | 0.144 | 0.073          | 0.147 |

| -20          | 0.174          | 0.36  | 0.202          | 0.405 |

| -15          | 0.452          | 0.82  | 0.52           | 0.99  |

| -10          | 1.075          | 1.67  | 1.222          | 2.139 |

| -5           | 2.31           | 3.15  | 2.619          | 4.196 |

| 0            | 4.68           | 5.69  | 5.208          | 7.686 |

| 5            | 8.89           | 9.98  | 9.84           | 11.59 |

| 10           | 13.46          | 12.78 | 13.62          | 12.36 |

| 15           | 19.19          | 15.34 | 19.36          | 15.33 |

| 20           | 24.54          | 21.20 | 24.83          | 21.07 |

## **CONCLUSIONS**

A matching using L-network has been discussed in order to boost the efficiency of the multiplier circuit at low power level. Theoretical approach to obtain value of the inductance and capacitance for certain impedance has been presented. Simulation further verified that the

© 2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

### www.arpnjournals.com

multiplier circuit produces more rectified output voltage at low input power when the matching network is applied to the circuit.

#### REFERENCES

- [1] Anchustegui Echearte I., Jimenez Lopez D., Gasulla Forner M., Giuppi F. and Georgiadis A. 2013. A high-efficiency matching technique for low power levels in RF harvesting

- [2] Avago Technologies, HSMS-2850. Surface Mount Zero Bias Schottky Detector Diodes.

- [3] Devi K., Sadasivam S., Din N. M. and Chakrabarthy C. K. 2011. Design of a 377 Ω patch antenna for ambient RF energy harvesting at downlink frequency of GSM 900. In: 2011 17<sup>th</sup> IEEE. Asia-Pacific Conference on Communications (APCC), pp. 492-495.

- [4] Hong S. S. B., Ibrahim R. B., Khir M. H. M., Zakariya M. A. B. and Daud H. 2013. Wi-Fi Energy Harvester for Low Power RFID Application. Progress In Electromagnetics Research C, Vol. 40, pp. 69-81.

- [5] Jabbar H., Song Y.S. and Jeong T.T. 2010. RF energy harvesting system and circuits for charging of mobile devices. IEEE Transactions on Consumer Electronics, Vol. 56, pp. 247–253.

- [6] Karthaus U. and Fischer M. 2003. Fully integrated passive uhf rfid transponder ic with 16.7-μ minimum rf input power. IEEE Journal of Solid-State Circuits, Vol. 38, pp. 1602–1608.

- [7] Keyrouz S., Visser H. J. and Tijhuis A. G. 2012. Ambient RF energy harvesting from DTV stations. In: Antennas and Propagation Conference (LAPC), Loughborough, pp. 1-4.

- [8] Kim S. 2011. RF energy harvesting techniques for wirelessly powered devices. In: 2011 IEEE MTT-S International Microwave Workshop Series on Intelligent Radio for Future Personal Terminals, IMWS-IRFPT 2011.

- [9] Matiko J. W., Grabham N. J., Beeby S. P. and Tudor M. J. 2014. Review of the application of energy harvesting in buildings. Measurement Science and Technology, Vol. 25, No. 1, 012002.

- [10] Merz C., Kupris G. and Niedernhuber M. 2014. A low power design for radio frequency energy harvesting applications. In: Wireless Systems within the Conferences on Intelligent Data Acquisition and

- Advanced Computing Systems: 2014 2nd International Symposium on Technology and Applications (IDAACS-SWS), pp. 74-78.

- [11] Mikeka Chomora, Hiroyuki Arai, Apostolos Georgiadis and Ana Collado 2011. DTV band micropower RF energy-harvesting circuit architecture and performance analysis. In: 2011 IEEE International Conference on RFID-Technologies and Applications (RFID-TA), pp. 561-567.

- [12] Muramatsu M. and Koizumi H. 2010. An experimental result using RF energy harvesting circuit with dickson charge pump. In: 2010 IEEE International Conference on Sustainable Energy Technologies, ICSET 2010.

- [13] Nintanavongsa P., Muncuk U., Lewis D. R. and Chowdhury K. R. 2012. Design optimization and implementation for RF energy harvesting circuits. Emerging and Selected Topics in, IEEE Journal on Circuits and Systems, Vol. 2, No. 1, pp. 24-33.

- [14] Pham B. L. and Pham A. V. 2013. Triple bands antenna and high efficiency rectifier design for RF energy harvesting at 900, 1900 and 2400 MHz. In Microwave Symposium Digest (IMS), 2013 IEEE MTT-S International, pp. 1-3.

- [15] Rhea R. 2006. The Yin-Yang of Matching: Part 1—Basic Matching Concepts. High Frequency Electronics, Vol. 5, No. 3.

- [16] Sajina Pradhan, Seong-Ro, Lee Sun-Kok Noh and Dong You Choi. 2014. Comparative Study of Rectenna for Electromagnetic Energy Harvesting. In: International Journal of Control and Automation, Vol. 1.7, No. 3, pp. 101-112.

- [17] Sogorb T., Llario J. V., Pelegri J., Lajara R. and Alberola J. 2008. Studying the feasibility of energy harvesting from broadcast RF station for WSN. In: Instrumentation and Measurement Technology Conference Proceedings, 2008. IMTC 2008. IEEE, pp. 1360-1363.

- [18] Toudeshki A., Mariun N., Hizam H. and Abdul Wahab N. I. 2014. Development of a New Cascade Voltage-Doubler for Voltage Multiplication. Chinese Journal of Engineering.

- [19] Zhang J., Huang Y. and Cao P. 2013. A wideband cross dipole rectenna for RF wireless harvesting. In: 7<sup>th</sup> European Conference on Antennas and Propagation (EuCAP), pp. 3063-3067.