# OPTIMIZATION OF PROCESS PARAMETER VARIATIONS ON THRESHOLD VOLTAGE IN ULTRATHIN PILLAR VERTICAL DOUBLE GATE MOSFET DEVICE

Khairil Ezwan Kaharudin<sup>1</sup>, Abdul Hamid Hamidon<sup>1</sup>, Fauziyah Salehuddin<sup>1</sup>, Muhammad Nazirul Ifwat Abd Aziz<sup>1</sup> and Ibrahim Ahmad<sup>2</sup>

<sup>1</sup>Micro and Nano electronics Research Group, Centre for Telecommunication Research and Innovation , Universiti Teknikal Malaysia Melaka, Durian Tunggal, Melaka, Malaysia

<sup>2</sup>Centre for Micro and Nano Engineering, College of Engineering, Universiti Tenaga Nasional, Kajang, Selangor, Malaysia E-Mail: <u>khairilezwan@yahoo.com.my</u>

### ABSTRACT

In the fabrication of MOSFET devices, the process parameters play a very important role in deciding the MOSFET device's characteristics. The process parameter variations may contribute a significant impact on the dopant profiles that directly affect the device characteristics. These variations cause significant unpredictability in the power and performance characteristics of the device that may cause the degradation of the device performance. Therefore, a special technique involving design and analytical experiments is required to identify the process parameters that contribute the most of these variations In this current study, the  $L_{27}$  orthogonal array of Taguchi method was utilized to optimize the variability of process parameters on threshold voltage ( $V_{TH}$ ) in Ultrathin Pillar Vertical Double Gate MOSFET Device. This work was initially performed by using Silvaco technology computer-aided design (TCAD) simulator consisted of a process simulator (ATHENA) and a device simulator (ATLAS). These two simulators were combined with the  $L_{27}$  orthogonal array of Taguchi method in order to obtain the robust design recipe. The results revealed that the halo implant tilt was the most dominant process parameter that had the strongest effect on threshold voltage ( $V_{TH}$ ) value. The most optimum  $V_{TH}$  value was observed to be 0.443 V and it is only 0.89% lower than the target or nominal value (0.447 V). This value is still within the predicted range of ITRS 2013 for low power (LP) multi-gate (MG) technology requirement in the year 2020.

Keywords: analysis of variance, taguchi method, threshold voltage, signal-to-noise ratio.

### INTRODUCTION

Over the past decades, the Metal Oxide Semiconductor Field Effect Transistor (MOSFET) has continually been scaled down in dimension and in channel length from micrometer to nanometer range as predicted by Moore's law. The MOSFET's size reduction is demanded due to the mass production of micro-technology devices. Furthermore, the size reduction of the MOSFET's device makes great improvement in MOSFET's operation (Taur and Ning, 1998). The main reason why MOSFET device has been attempted to be scaled down is to pack more and more MOSFET devices in a given chip area.

Designing a conventional planar MOSFET device with a very small channel length, especially for below the 22nm technology node is very complicated and difficult. An attempt of reducing the physical gate (Lg) of conventional MOSFET device has resulted in the drain region to be much closer to the source region, thereby introducing the short channel effects (SCEs) which eventually lead to the increase of leakage current ( $I_{OFF}$ ). One of the popular methods to circumvent this matter is by implementing a combination of high permittivity (high-k) dielectric material and metal gate in MOSFET's structure. However, in this current work, the traditional silicon dioxide (SiO<sub>2</sub>) and polysilicon material are still being used by utilizing vertical DG-MOSFET design concept.

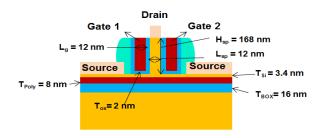

The vertical DG-MOSFET device consists of ultrathin silicon (Si) pillar that isolates the two polysilicon gates as depicted in Figure-1. The main purpose of double gates is to control the channel from both sides in order to produce a better electrostatic control over the channel (Kaharudin *et al.*, 2014). The vertical shape of the ultrathin Si-pillar will boost the saturation current or the drive current ( $I_{ON}$ ).

Figure-1. Vertical DG-MOSFET layout.

Since the drain region of vertical DG-MOSFET device is located at the top, the effective channel length

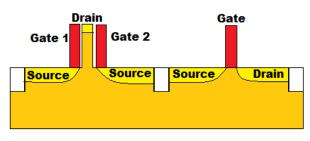

(Lc) does not depend on the physical gate length (Lg). Therefore, the SCEs phenomenon will be well mitigated and suppressed. Another advantage of vertical DG-MOSFET device is it can be easily integrated with planar MOSFET as depicted in Figure-2 (Masahara *et al.*, 2004).

At present day, MOSFET's process invariability utilizes ion implantation into the channel region, which eventually alters the doping profile near the surface of silicon substrate (Kang and Leblebici, 2003). Ion implantation technique involves doping concentration, doping energy and tilt angle. By altering the dosage, energy and rotation of these implants, the profile and characteristics of the MOSFET device will also be affected (Ninomiya et al., 2009), (Wang et al., 2005). One of the most important electrical characteristics of MOSFET's device is its threshold voltage ( $V_{TH}$ ).  $V_{TH}$  is defined as the minimum voltage that is required to create a channel between the source and the drain. In other words, it is the minimum voltage required for strong inversion to occur (Croon et al., 2002). V<sub>TH</sub> value is strongly influenced by process parameters variation. Therefore, the analysis of variability has become a very important tool in order to predict the response variation in a very early design cycle due to process parameter spreads (Nassif et al., 1984). The variations will impact the performance of device which may lead to the degradation of yield in modern technologies and application (Sylvester et al., 2008).

Figure-2. Integration with planar MOSFET.

In the previous research, the  $L_{12}$  orthogonal array of Taguchi method has been utilized to optimize the process parameter variations for higher on-current (I<sub>ON</sub>) in the vertical double-gate MOSFET device (Kaharudin et al., 2014). The result shows that Taguchi method was capable of predicting the robust process recipe for the device in obtaining the highest I<sub>ON</sub> value. This paper emphasizes on utilizing L<sub>27</sub> orthogonal array of Taguchi method that consists of thirteen process parameters which are substrate implant dose, V<sub>TH</sub> implant dose, V<sub>TH</sub> implant energy, halo implant energy, halo implant tilt, source/drain (S/D) implant dose, compensation implant dose, compensation implant energy and etc. The gate oxide temperature and polysilicon oxidation temperature are selected as noise factors in order to get the optimum results. The main objective of the current work is to acquire the nominal value of V<sub>TH</sub> as predicted by International Technology Roadmap Semiconductor (ITRS) 2013. Specifically, the threshold voltage ( $V_{TH}$ ) value must be within  $\pm 12.7\%$  of low power (LP) multi-gate (MG) technology requirement in ITRS 2013 prediction (0.447V) for year 2020 as listed in Table-1 (ITRS, 2013).

| <b>Table-1.</b> ITRS 2013 Prediction for Multi-gate (MG) |

|----------------------------------------------------------|

| Technology (ITRS, 2013).                                 |

| Device characteristic                | ITRS 2013 Prediction for<br>low power (LP) Multi-<br>gate (MG) requirement in<br>year 2020 |

|--------------------------------------|--------------------------------------------------------------------------------------------|

| Physical Gate Length<br>(Lg)         | 12.2 nm                                                                                    |

| Threshold Voltage (V <sub>TH</sub> ) | 0.447 V                                                                                    |

| Drive Current (I <sub>ON</sub> )     | $\geq$ 533 $\mu$ A/ $\mu$ m                                                                |

| Leakage Current (I <sub>OFF</sub> )  | $\leq$ 20 pA/ $\mu$ m                                                                      |

### MATERIAL AND METHODS

### Virtual fabrication

The process started with selection of a p-type silicon with <100> orientation as the main substrate by implanting 1 x 10<sup>14</sup> atom/cm<sup>3</sup> of boron into silicon substrate. Buried oxide (BOX) of 16nm (t<sub>BOX</sub>) was then developed beneath the silicon substrate. The remaining silicon substrate at the top was etched in order to form an ultrathin Si-pillar with length of 12 nm (Lsp) and height of 168 nm (Hsp). The function of ultrathin Si-pillar was to form a very sharp vertical channel that could increase the drive current (I<sub>ON</sub>). The virtual process was followed by the gate oxidation process at temperature of 920° C. Since the device was an n-channel type, 9.81 x 10<sup>12</sup> atom/cm<sup>3</sup> of boron was implanted into the substrate at 20 Kev energy and 7° tilt in order to form p+ region.

Polysilicon material was then deposited at the top of the gate oxide. After that, both polysilicon and polysilicon oxide were etched away to form a very thin gate with length of 12nm (Lg). In order to enhance performance of the device,  $2.61 \times 10^{13}$  atom/cm<sup>3</sup> concentration of indium was doped at energy level of 170 Kev and tilt angle of 24° (Halo implantation). Halo implantation was followed by depositing sidewall spacers. Sidewall spacers were used as a mask for source/drain implantation process. Arsenic atom with concentration of  $1.22 \times 10^{20}$  atom/cm<sup>3</sup> was implanted in order to supply free electron to form n+ region as conductive channel.

Compensation implantation was utilized later by implanting phosphor dosage of  $2.51 \times 10^{12}$  atom/cm<sup>3</sup> with energy level of 60 Kev and tilt angle of 7°. The function of compensation implantation was to reduce parasitic effects that could increase the leakage current (I<sub>OFF</sub>). Next, silicide (CoSi) was formed on the source and drain region by sputtering cobalt on silicon surface. The vast majority of the silicide exhibit metallic conductivity and the silicide-

silicon junction will behave as a metal-semiconductor contact (Chen, 2005).

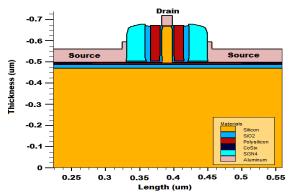

This device was then connected with aluminum metal. The aluminum layer was deposited on the top of the Intel-Metal Dielectric (IMD) and unwanted aluminum was etched to develop the contacts (Kaharudin *et al.*, 2014), (Salehuddin *et al.*, 2014). The procedure was completed after the metallization and etching were performed for electrode formation, and the bonding pads were opened. The final structure of the device was completed by mirroring the right-hand side structure. The completed structure of ultrathin Si-pillar vertical DG-MOSFET device is illustrated as in Figure-3.

Figure-3. Structure of vertical DG-MOSFET device.

| Exp |   |   | Pro | cess par | ameter | level |   |   |   |   |   |   |   |

|-----|---|---|-----|----------|--------|-------|---|---|---|---|---|---|---|

| No. | Α | В | С   | D        | Е      | F     | G | Н | J | K | L | Μ | Ν |

| 1   | 1 | 1 | 1   | 1        | 1      | 1     | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 2   | 1 | 1 | 1   | 1        | 2      | 2     | 2 | 2 | 2 | 2 | 2 | 2 | 2 |

| 3   | 1 | 1 | 1   | 1        | 3      | 3     | 3 | 3 | 3 | 3 | 3 | 3 | 3 |

| 4   | 1 | 2 | 2   | 2        | 1      | 1     | 1 | 2 | 2 | 2 | 3 | 3 | 3 |

| 5   | 1 | 2 | 2   | 2        | 2      | 2     | 2 | 3 | 3 | 3 | 1 | 1 | 1 |

| 6   | 1 | 2 | 2   | 2        | 3      | 3     | 3 | 1 | 1 | 1 | 2 | 2 | 2 |

| 7   | 1 | 3 | 3   | 3        | 1      | 1     | 1 | 3 | 3 | 3 | 2 | 2 | 2 |

| 8   | 1 | 3 | 3   | 3        | 2      | 2     | 2 | 1 | 1 | 1 | 3 | 3 | 3 |

| 9   | 1 | 3 | 3   | 3        | 3      | 3     | 3 | 2 | 2 | 2 | 1 | 1 | 1 |

| 10  | 2 | 1 | 2   | 3        | 1      | 2     | 3 | 1 | 2 | 3 | 1 | 2 | 3 |

| 11  | 2 | 1 | 2   | 3        | 2      | 3     | 1 | 2 | 3 | 1 | 2 | 3 | 1 |

| 12  | 2 | 1 | 2   | 3        | 3      | 1     | 2 | 3 | 1 | 2 | 3 | 1 | 2 |

| 13  | 2 | 2 | 3   | 1        | 1      | 2     | 3 | 2 | 3 | 1 | 3 | 1 | 2 |

| 14  | 2 | 2 | 3   | 1        | 2      | 3     | 1 | 3 | 1 | 2 | 1 | 2 | 3 |

| 15  | 2 | 2 | 3   | 1        | 3      | 1     | 2 | 1 | 2 | 3 | 2 | 3 | 1 |

| 16  | 2 | 3 | 1   | 2        | 1      | 2     | 3 | 3 | 1 | 2 | 2 | 3 | 1 |

| 17  | 2 | 3 | 1   | 2        | 2      | 3     | 1 | 1 | 2 | 3 | 3 | 1 | 2 |

| 18  | 2 | 3 | 1   | 2        | 3      | 1     | 2 | 2 | 3 | 1 | 1 | 2 | 3 |

| 19  | 3 | 1 | 3   | 2        | 1      | 3     | 2 | 1 | 3 | 2 | 1 | 3 | 2 |

| 20  | 3 | 1 | 3   | 2        | 2      | 1     | 3 | 2 | 1 | 3 | 2 | 1 | 3 |

| 21  | 3 | 1 | 3   | 2        | 3      | 2     | 1 | 3 | 2 | 1 | 3 | 2 | 1 |

| 22  | 3 | 2 | 1   | 3        | 1      | 3     | 2 | 2 | 1 | 3 | 3 | 2 | 1 |

### Table-2. L<sub>27</sub> Orthogonal array Taguchi method.

### Taguchi L27 orthogonal array method

Taguchi method was utilized in order to optimize process parameter variations on threshold voltage ( $V_{TH}$ ) in vertical DG-MOSFET device. The Taguchi method consists of a special orthogonal array that consists of twenty seven rows of the experiment. The Taguchi method has a capability of selecting the best level's combination of process parameters with less number of experiments. In the current research, Taguchi L<sub>27</sub> orthogonal array was used to investigate the impact of 13 process parameters on threshold voltage ( $V_{TH}$ ). The design of experiments (DoE) of 27 experiment rows with a different combination level of process parameters was constructed in Table-2.

Ę,

ARPN Journal of Engineering and Applied Sciences ©2006-2016 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

| 23 | 3 | 2 | 1 | 3 | 2 | 1 | 3 | 3 | 2 | 1 | 1 | 3 | 2 |

|----|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 24 | 3 | 2 | 1 | 3 | 3 | 2 | 1 | 1 | 3 | 2 | 2 | 1 | 3 |

| 25 | 3 | 3 | 2 | 1 | 1 | 3 | 2 | 3 | 2 | 1 | 2 | 1 | 3 |

| 26 | 3 | 3 | 2 | 1 | 2 | 1 | 3 | 1 | 3 | 2 | 3 | 2 | 1 |

| 27 | 3 | 3 | 2 | 1 | 3 | 2 | 1 | 2 | 1 | 3 | 1 | 3 | 2 |

The nominal or target value of  $V_{TH}$  is expected to be closed to 0.447 V as predicted by ITRS 2013 for low power (LP) multi-gate (MG) technology in the year 2020. A total of 108 runs are required in order to optimize the process parameters variation in Vertical DG-MOSFET device. All the values of process parameters and noise factors with their corresponding levels are listed in Table-3 and Table-4.

| Sym. | Process<br>parameter              | Units                | Level 1 | Level 2 | Level 3 |

|------|-----------------------------------|----------------------|---------|---------|---------|

| А    | Substrate<br>Implant Dose         | atom/cm <sup>3</sup> | 1E14    | 1.03E14 | 1.06E14 |

| В    | V <sub>TH</sub> Implant Dose      | atom/cm <sup>3</sup> | 9.81E12 | 9.84E12 | 9.87E12 |

| С    | V <sub>TH</sub> Implant<br>Energy | kev                  | 20      | 21      | 22      |

| D    | V <sub>TH</sub> Implant Tilt      | degree               | 7       | 10      | 13      |

| Е    | Halo Implant<br>Dose              | atom/cm <sup>3</sup> | 2.61E13 | 2.64E13 | 2.67E13 |

| F    | Halo Implant<br>Energy            | kev                  | 170     | 172     | 174     |

| G    | Halo Implant Tilt                 | degree               | 24      | 27      | 30      |

| Н    | S/D Implant Dose                  | atom/cm <sup>3</sup> | 1.22E20 | 1.25E20 | 1.28E20 |

| J    | S/D Implant<br>Energy             | kev                  | 43      | 45      | 47      |

| K    | S/D Implant Tilt                  | degree               | 80      | 83      | 86      |

| L    | Compensation<br>Implant Dose      | atom/cm <sup>3</sup> | 2.51E12 | 2.54E12 | 2.57E12 |

| М    | Compensation<br>Implant Energy    | kev                  | 60      | 62      | 64      |

| Ν    | Compensation<br>Implant Tilt      | degree               | 7       | 10      | 13      |

Table-3. Process parameters and their levels.

Table-4. Noise factors and their levels.

| Symbol | Noise factor                         | Units | Level 1 | Level 2 |

|--------|--------------------------------------|-------|---------|---------|

| U      | Gate Oxidation<br>Temperature        | Cº    | 920     | 923     |

| V      | Polysilicon Oxidation<br>Temperature | Co    | 870     | 873     |

### **RESULTS AND DISCUSSIONS**

The electrical characterization of the device was then simulated by using ATLAS module. Next, the  $L_{27}$  orthogonal array of Taguchi method was implemented in order to obtain the possible nominal value of the threshold voltage (V<sub>TH</sub>).

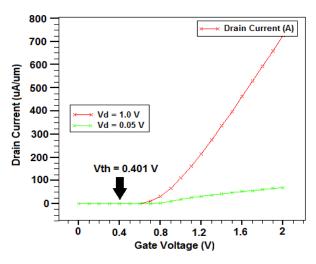

### Characterization of vertical DG-MOSFET device

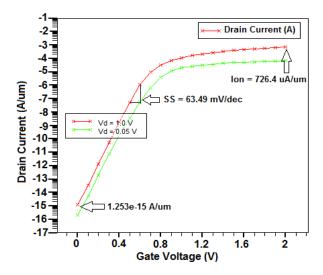

Figure-4 shows the graph of drain current (I<sub>D</sub>) versus gate voltage (V<sub>G</sub>) at drain voltage V<sub>D</sub> = 0.05 V and voltage V<sub>D</sub> = 1.0 V for vertical DG-MOSFET device. The expected nominal value of threshold voltage (V<sub>TH</sub>) for this device is 0.447 V (ITRS, 2013). However, the V<sub>TH</sub> value extracted from the graph was only 0.401 V. There was a decrease of 0.046 V from the nominal or target value.

## **ARPN** Journal of Engineering and Applied Sciences

©2006-2016 Asian Research Publishing Network (ARPN). All rights reserved

www.arpnjournals.com

Figure-4. Graph of drain current (I<sub>D</sub>) versus gate voltage (V<sub>G</sub>).

Figure-5 shows the graph of subthreshold drain current (I<sub>D</sub>) versus gate voltage (V<sub>G</sub>) at drain voltage  $V_D$  = 0.05V and  $V_D = 1.0V$  for vertical DG-MOSFET device. The value of off-leakage current (IOFF) and drive current (I<sub>ON</sub>) were extracted from the graph.

Figure-5. Graph of subthreshold drain current (I<sub>D</sub>) versus gate voltage (V<sub>G</sub>).

From the graph, it was observed that the value of drive current (I<sub>ON</sub>) was 726.4 µA/µm. Meanwhile, the offleakage current ( $I_{OFF}$ ) was observed to be 1.253e-15 A/µm. A very low leakage current (IOFF) indicates a better suppression of short channel effect (SCE) problems. The value of subthreshold swing (SS) was calculated by using (1) (Ferrain et al., 2013):

$$SS = \left[\frac{dV_{GS}}{d(\log_{10}I_{DS})}\right]$$

(1)

The initial value of subthreshold swing (SS) was observed to be 63.49 mV/dec. Subthreshold swing (SS) is regarded as an important characteristic in MOSFET's device as it indicates how fast the switching transition from "ON" to "OFF" state or vice versa.

### Signal-to-noise ratio (SNR) analysis

After 27 runs of experiment have been performed, the next step is to determine the most significant process parameters that contribute the most impact on device characteristics. The L<sub>27</sub> orthogonal array analysis for threshold voltage (V<sub>TH</sub>) values recorded in Table-5.

| Table-5. Threshold voltage values for vertical DG- |

|----------------------------------------------------|

| MOSFET device.                                     |

| Experiment | Tł                                | nreshold vo                | tage, VTH (    | (V)                        |

|------------|-----------------------------------|----------------------------|----------------|----------------------------|

| no.        | <b>V</b> <sub>ТН1</sub><br>(U1V1) | V <sub>TH2</sub><br>(U1V2) | Vтнз<br>(U2V1) | V <sub>TH4</sub><br>(U2V2) |

| 1          | 0.401                             | 0.412                      | 0.419          | 0.434                      |

| 2          | 0.389                             | 0.402                      | 0.407          | 0.423                      |

| 3          | 0.347                             | 0.358                      | 0.364          | 0.38                       |

| 4          | 0.396                             | 0.407                      | 0.413          | 0.429                      |

| 5          | 0.371                             | 0.384                      | 0.39           | 0.407                      |

| 6          | 0.339                             | 0.351                      | 0.357          | 0.373                      |

| 7          | 0.38                              | 0.392                      | 0.399          | 0.414                      |

| 8          | 0.375                             | 0.388                      | 0.392          | 0.41                       |

| 9          | 0.329                             | 0.341                      | 0.348          | 0.363                      |

| 10         | 0.31                              | 0.322                      | 0.328          | 0.342                      |

| 11         | 0.412                             | 0.424                      | 0.431          | 0.447                      |

| 12         | 0.381                             | 0.423                      | 0.4            | 0.414                      |

| 13         | 0.317                             | 0.328                      | 0.335          | 0.35                       |

| 14         | 0.422                             | 0.435                      | 0.444          | 0.46                       |

| 15         | 0.397                             | 0.439                      | 0.417          | 0.431                      |

| 16         | 0.325                             | 0.336                      | 0.342          | 0.357                      |

| 17         | 0.416                             | 0.428                      | 0.435          | 0.451                      |

| 18         | 0.406                             | 0.448                      | 0.425          | 0.439                      |

| 19         | 0.369                             | 0.381                      | 0.387          | 0.403                      |

| 20         | 0.317                             | 0.328                      | 0.335          | 0.349                      |

| 21         | 0.421                             | 0.433                      | 0.442          | 0.454                      |

| 22         | 0.375                             | 0.387                      | 0.394          | 0.407                      |

| 23         | 0.338                             | 0.349                      | 0.356          | 0.37                       |

ARPN Journal of Engineering and Applied Sciences ©2006-2016 Asian Research Publishing Network (ARPN). All rights reserved.

# CO.

### www.arpnjournals.com

| 24 | 0.433 | 0.445 | 0.454 | 0.468 |

|----|-------|-------|-------|-------|

| 25 | 0.374 | 0.385 | 0.393 | 0.408 |

| 26 | 0.327 | 0.338 | 0.346 | 0.359 |

| 27 | 0.433 | 0.446 | 0.456 | 0.47  |

Where as:

$$\mu = \frac{Y_i + \dots + Y_n}{n} \tag{3}$$

and

After obtaining all the results, all the process parameters of Vertical DG-MOSFET device were optimized by using Taguchi method. Taguchi method was assigned to analyze the V<sub>TH</sub> values using SNR analysis of Nominal-the-best. The SNR (Nominal-the-better),

$$\eta$$

can be expressed as (Phadke, 1998):

$$\eta = 10 \log_{10} \left[ \frac{\mu^2}{\sigma^2} \right]$$

(2)

$$\sigma^{2} = \frac{\sum_{i=1}^{n} (Y_{i} - \mu)^{2}}{n - 1}$$

(4)

where *n* is number of tests and *yi* is the experimental values of  $V_{TH}$ . By utilizing formula given in (2), the SNR for each row of experiments were computed and recorded in Table-6.

| Exp. No | Mean  | Variance | SNR<br>(Mean),<br>dB | SNR<br>(Nominal-the-best), dB |

|---------|-------|----------|----------------------|-------------------------------|

| 1       | 0.417 | 1.91E-04 | -7.61                | 29.58                         |

| 2       | 0.405 | 1.98E-04 | -7.85                | 29.20                         |

| 3       | 0.362 | 1.90E-04 | -8.82                | 28.40                         |

| 4       | 0.411 | 1.90E-04 | -7.72                | 29.50                         |

| 5       | 0.388 | 2.23E-04 | -8.22                | 28.29                         |

| 6       | 0.355 | 2.00E-04 | -9.00                | 27.99                         |

| 7       | 0.396 | 2.02E-04 | -8.04                | 28.91                         |

| 8       | 0.391 | 2.09E-04 | -8.15                | 28.65                         |

| 9       | 0.345 | 2.02E-04 | -9.24                | 27.72                         |

| 10      | 0.326 | 1.77E-04 | -9.75                | 27.77                         |

| 11      | 0.429 | 2.14E-04 | -7.36                | 29.34                         |

| 12      | 0.405 | 3.35E-04 | -7.86                | 26.89                         |

| 13      | 0.333 | 1.91E-04 | -9.56                | 27.63                         |

| 14      | 0.440 | 2.55E-04 | -7.13                | 28.81                         |

| 15      | 0.421 | 3.39E-04 | -7.51                | 27.19                         |

| 16      | 0.340 | 1.78E-04 | -9.37                | 28.13                         |

| 17      | 0.433 | 2.14E-04 | -7.28                | 29.42                         |

| 18      | 0.430 | 3.35E-04 | -7.34                | 27.41                         |

| 19      | 0.385 | 2.00E-04 | -8.29                | 28.70                         |

| 20      | 0.332 | 1.80E-04 | -9.57                | 27.89                         |

| 21      | 0.438 | 1.95E-04 | -7.18                | 29.92                         |

| 22      | 0.391 | 1.79E-04 | -8.16                | 29.31                         |

| 23      | 0.353 | 1.80E-04 | -9.04                | 28.42                         |

| 24      | 0.450 | 2.18E-04 | -6.94                | 29.68                         |

| 25      | 0.390 | 2.05E-04 | -8.18                | 28.71                         |

VOL. 11, NO. 6, MARCH 2016

### ISSN 1819-6608

ARPN Journal of Engineering and Applied Sciences ©2006-2016 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

| 26 | 0.343 | 1.82E-04 | -9.31 | 28.10 |

|----|-------|----------|-------|-------|

| 27 | 0.451 | 2.45E-04 | -6.91 | 29.20 |

Generally, the experiment row, which has the highest SNR will be recognized as the best performance characteristics. Based on Table 6, it was observed that experiment row 21 had the highest SNR value for  $V_{TH}$  which was observed to be 29.92dB. This indicates that

experiment of row 21 possessed the best insensitivity for  $V_{TH}$ . Since the design of experiment (DoE) was orthogonally constructed, the SNR of each process parameters can be separated out. The SNR (Nominal-thebest) was summarized in Table-7.

| Process    | Sig     |         |         |                  |

|------------|---------|---------|---------|------------------|

| parameters | Level 1 | Level 2 | Level 3 | Overall mean SNR |

| А          | 28.69   | 28.06   | 28.88   |                  |

| В          | 28.63   | 28.54   | 28.47   |                  |

| С          | 28.84   | 28.42   | 28.38   |                  |

| D          | 28.53   | 28.58   | 28.52   |                  |

| Е          | 28.69   | 28.68   | 28.27   |                  |

| F          | 28.21   | 28.72   | 28.71   | 28.55            |

| G          | 29.37   | 28.26   | 28.00   |                  |

| Н          | 28.57   | 28.58   | 28.50   |                  |

| J          | 28.49   | 28.65   | 28.50   |                  |

| K          | 28.63   | 28.52   | 28.49   |                  |

| L          | 28.43   | 28.56   | 28.65   |                  |

| М          | 28.42   | 28.60   | 28.61   |                  |

| Ν          | 28.62   | 28.48   | 28.54   |                  |

Table-7. SNR of process parameters in vertical DG-MOSFET device.

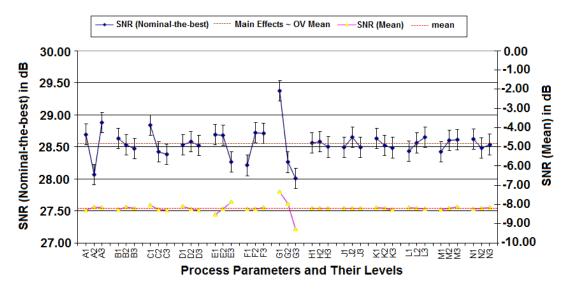

Based on Table-7, the factor effects graph for SNR (Nominal-the-best) was plotted as illustrated in Figure-6. The dashed horizontal lines in both graphs represent the overall mean of SNR (Nominal-the-best) and SNR (Mean) which were 28.55 dB and -8.20 dB.

(OR

### www.arpnjournals.com

From Figure-6, it was observed that factor A3, B1, C1, D2, E1, F2, G1, H2, J2, K1, L3, M3 and N1 have been selected as the optimum value for  $V_{TH}$  due to their highest SNR. Factor A, B, C, D, E, F, G, H, J, K, L, M and N represents Substrate Implant Dose,  $V_{TH}$  Implant Dose,  $V_{TH}$  Implant Energy,  $V_{TH}$  Implant Tilt, Halo Implant dose, Halo Implant Energy, Halo Implant Tilt, S/D Implant Dose, S/D Implant Energy, S/D Implant Tilt, Compensation Implant Dose, Compensation Implant Energy and Compensation Implant Tilt accordingly.

### Analysis of Variance (ANOVA)

The common practical method in investigating the relative effect of different process parameters on  $V_{\text{TH}}$

were realized by decomposition of variance which was called analysis of variance (ANOVA) (Salehuddin *et al.*, 2013). ANOVA computes parameters which are known as sum of squares (SSQ), degree of freedom (DF), variance or mean square (MS), F-value and percentage of effect on each factor or process parameter. The results of ANOVA for  $V_{TH}$  in Vertical DG-MOSFET device are listed in Table-8. F-test was statistically conducted in order to provide a decision at some confidence level to determine the significance of certain factor (process parameter). A larger F-value implies that the variation of certain process parameter has contributed a large effect on the device performance (Kamaruddin *et al.*, 2010).

| Sym. | DF | SSQ | MS | F-<br>value | Factor<br>effects on<br>SNR (%) | Factor<br>effects on<br>mean (%) |

|------|----|-----|----|-------------|---------------------------------|----------------------------------|

| А    | 2  | 3   | 2  | 9402        | 19                              | 1                                |

| В    | 2  | 0   | 0  | 333         | 1                               | 0                                |

| С    | 2  | 1   | 1  | 3316        | 7                               | 2                                |

| D    | 2  | 0   | 0  | 54          | 0                               | 1                                |

| Е    | 2  | 1   | 1  | 3030        | 6                               | 9                                |

| F    | 2  | 2   | 1  | 4361        | 9                               | 0                                |

| G    | 2  | 10  | 5  | 27290       | 55                              | 87                               |

| Н    | 2  | 0   | 0  | 95          | 0                               | 0                                |

| J    | 2  | 0   | 0  | 413         | 1                               | 0                                |

| K    | 2  | 0   | 0  | 274         | 1                               | 0                                |

| L    | 2  | 0   | 0  | 598         | 1.20                            | 0.07                             |

| М    | 2  | 0   | 0  | 597         | 1                               | 0                                |

| Ν    | 2  | 0   | 0  | 239         | 0                               | 0                                |

At least 95% confidence

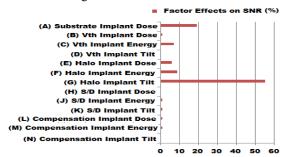

According to Table-8, the most dominant process parameters with respect to output response (V<sub>TH</sub>) were observed to be factor A (Substrate Implant Dose = 19%) and G (Halo Implant Tilt = 55%). Therefore, these factors should be set at "best setting" and cannot be used as adjustment factor. Meanwhile factor C (VTH Implant Energy = 7%), E (Halo Implant Dose = 6%) and F (Halo Implant Energy = 9%) were observed to be significant factors. Whereas, factor E (Halo Implant Dose) was described as an adjustment factor due to its large effect on mean (9%) and small effect on variance (6%) if compared to other factors. The percentage of factor effects on SNR indicates the priority of a factor (process parameter) to reduce variation (Salehuddin et al., 2014). A factor with high percentage of contribution and a small variance (mean square) has a great influence on device's performance (Nalbant *et al.*, 2007). The percentages of factor effect on SNR of all factors are visualized as in the pareto chart in Figure-7.

Figure-7. Pareto plot of factor effects on SNR for  $V_{TH}$ .

### **CONFIRMATION RUN**

Confirmation run is the final step in the design of experiment (DoE) process. The main purpose of the confirmation run is to validate the results retrieved during analysis phase (Phadke, 1998). Confirmation run was performed by conducting an actual simulation test while using the overall best level setting of process parameters as predicted by Taguchi method before. Table-9 shows the overall best setting of process parameters in Vertical DG-MOSFET device.

| Sym. | Process parameter              | Units                | Best value |  |

|------|--------------------------------|----------------------|------------|--|

| Α    | Substrate implant dose         | atom/cm <sup>3</sup> | 1.06E14    |  |

| В    | V <sub>TH</sub> Implant Dose   | atom/cm <sup>3</sup> | 9.81E12    |  |

| С    | V <sub>TH</sub> Implant Energy | kev                  | 20         |  |

| D    | $V_{TH}$ Implant Tilt          | degree               | 10         |  |

| Е    | Halo Implant Dose              | atom/cm <sup>3</sup> | 2.61E13    |  |

| F    | Halo Implant Energy            | kev                  | 172        |  |

| G    | Halo Implant Tilt              | degree               | 24         |  |

| Н    | S/D Implant Dose               | atom/cm <sup>3</sup> | 1.25E20    |  |

| J    | S/D Implant Energy             | kev                  | 45         |  |

| K    | S/D Implant Tilt               | degree               | 80         |  |

| L    | Compensation Implant Dose      | atom/cm <sup>3</sup> | 2.57E12    |  |

| М    | Compensation Implant Energy    | kev                  | 64         |  |

| Ν    | Compensation Implant Tilt      | degree               | 7          |  |

**Table-9.** Overall best setting of process parameters.

The confirmation run was then conducted by utilizing ATHENA and ATLAS module. The electrical characteristic results of the confirmation run are listed in Table-10. Before the optimization approaches, the best SNR (Nominal-the-best) was 29.92 dB at experiment row 21 in Table-6. Whereas the variance was 1.95E-04 V and mean for  $V_{TH}$  was 0.438 V. There was a decrease of 2.01% in this  $V_{TH}$  value from the nominal value, 0.447 V (ITRS, 2013).

Table-10. Final results of confirmation run for threshold voltage.

|                  | Threshold        | SNR              | SNR              |        |                        |

|------------------|------------------|------------------|------------------|--------|------------------------|

| V <sub>TH1</sub> | V <sub>TH2</sub> | V <sub>TH3</sub> | V <sub>TH4</sub> | (Mean) | (Nominal-<br>the-best) |

| 0.409            | 0.421            | 0.429            | 0.443            | -7.50  | 30.32                  |

After the optimization approaches, the SNR (Nominal-the-best) and SNR (Mean) of  $V_{TH}$  for Vertical DG-MOSFET device was observed to be 30.32 dB and -7.50 dB respectively. These values are well within the predicted range. For SNR (Nominal-the-best), 30.32 dB is within the predicted SNR range of 30.74 to 29.89 dB (30.32±0.42 dB). Meanwhile, for SNR (Mean), -7.50 dB is within the predicted SNR range of -7.24 to -7.77 dB (-7.50±0.27 dB). The SNR (Nominal-the-best), 30.32 dB is observed to be the highest value among the others in Table VI which indicates the process parameters variation have been statistically optimized by Taguchi method.

The variance and threshold voltage ( $V_{TH}$ ) for the device after optimization approaches were 2.04E-04 and 0.443 V respectively. The results show that the variance is slightly increased and  $V_{TH}$  value is closer to the nominal

value (target). The  $V_{TH}$  value is only 0.89% lower than the target or nominal value (0.447 V). This  $V_{TH}$  value (0.443 V) is still within the predicted range of ITRS 2013 for low power (LP) multi-gate (MG) technology requirement in year 2020. These show that Taguchi method is able to predict the optimum solution in finding the Vertical DG-MOSFET fabrication recipe with appropriate threshold voltage (V<sub>TH</sub>) value.

Several device characteristics of the vertical double-gate MOSFET device were recorded and compared to the ITRS 2013 prediction and the real fabrication results. The detail comparison of the results with the ITRS 2013 prediction and the real fabrication process is listed in Table-11. It was observed that there is a slight improvement of the device characteristics when the Taguchi method was applied for optimization approach.

The subthreshold swing (SS) value is desired to be small (55-65 mV/dec) for faster switching operation.

Meanwhile, the on-current (ION) is desired to be as large as possible for better drive capability.

Table-11. Comparison of the results with ITRS 2013 and the real fabrication process.

| Electrical<br>responses    | Results from<br>this works | Results from real<br>fabrication (Masahara <i>el</i><br><i>al.</i> , 2004) | ITRS 2013 Prediction<br>(ITRS, 2013) |  |

|----------------------------|----------------------------|----------------------------------------------------------------------------|--------------------------------------|--|

| $V_{TH}(V)$                | 0.443                      | 0.430                                                                      | ±12.7% of 0.447                      |  |

| $I_{ON}$ ( $\mu A/\mu m$ ) | 696.6                      | 570                                                                        | ≥ 533                                |  |

| SS (mV/dec)                | 63.64                      | 69.8                                                                       | -                                    |  |

### CONCLUSIONS

In conclusion, the optimum solution in obtaining the desired threshold voltage (V<sub>TH</sub>) value was successfully predicted by the combination of process simulation, device simulation and the L<sub>27</sub> orthogonal array of Taguchi method. These tools are capable of predicting the process recipe of the device before it undergoes to real fabrication. Thus, the cost and time can be saved efficiently by the early prediction of the robust recipe. The threshold voltage  $(V_{TH})$  is the main response investigated in this project as it is regarded as the main factor in determining the functionality of Vertical DG-MOSFET device. The L<sub>27</sub> orthogonal array of Taguchi method design is utilized to be a systematic platform in studying the main effect of multiple factors (process parameters) upon threshold voltage (V<sub>TH</sub>). Based on ANOVA method, the process parameters that contribute the most impact on threshold voltage (V<sub>TH</sub>) were found to be and halo implant tilt (55%), substrate implant dose (19%), Halo Implant Energy (9%), V<sub>TH</sub> Implant Energy (7%) and Halo Implant Dose (6%) whereas the halo implant dose was described as an adjustment factor. The final results indicate that the VTH value is closer to the nominal value (target). The V<sub>TH</sub> value (0.443 V) is observed to be only 0.89% lower than the target or nominal value (0.447 V) and it is still within the predicted range of ITRS 2013 for low power (LP) multi-gate (MG) technology requirement in the year 2020.

### ACKNOWLEDGEMENT

The authors would like to thank to the Ministry of Higher Education (MOHE) and Faculty of Electronics and Computer Engineering (FKEKK), Universiti Teknikal Malaysia Melaka (UTeM) for sponsoring this study under the research grants (PJP/2014/FKEKK (6B)/S01341) and FRGS (RACE)/2012/FKEKK/TK02/02/2 F00148.

### REFERENCES

Chen, L. J. 2008. Metal Silicides: An Integral Part of Microelectronics. Journal of the Minerals, Metals and Materials Society (TMS), 41, pp. 319-339.

Croon, J. A., Augendre, E., Decoutre, S., Sansen, W., Maes, H. E. 2002. Influence of Doping Profile and Halo

Implantation on the Threshold Voltage Mismatch of a 0.13  $\mu$ m CMOS Technology. European Solid-state Device Conference, pp.579-582.

Ferain, I., Colinge, C. A., Colinge, J. P. 2011. Multigate Transistors as the Future of Classical Metal-Oxide-Semiconductor Field-Effect Transistors. Nature. 479, pp. 310-316.

ITRS 2013 Report; http://www.itrs.net

Kaharudin, K., Hamidon, A. H., Salehuddin, F. 2014. Impact of Height of Silicon Pillar on Vertical DG-MOSFET Device. International Journal of Computer, Information, Systems and Control Engineering. 8(6), pp. 576-580.

Kaharudin, K., Hamidon, A. H., Salehuddin, F. 2014. Implementation of Taguchi Modeling for Higher Drive Current (I<sub>ON</sub>) in Vertical DG-MOSFET Device. Journal of Telecommunication, Electronics and Computer Engineering. 6(2), pp.11-17.

Kamaruddin, S., Khan, Z. A., Foong, S. H. 2010. Application of Taguchi Method in the Optimization of Injection Moulding Parameters for Manufacturing Products from Plastic Blend. International Journal of Engineering and Technology, 2(6), pp.574-580.

Kang, S and Leblebici, Y. 2003. CMOS Digital Intergrated Circuit: Analysis and Design. McGarw-Hill Higher Companies, third ed.

Masahara, M *et al.* 2004. Ultrathin Channel Vertical DG MOSFET Fabricated by Using Ion-Bombardment-Retarded Etching. IEEE Transactions on Electron Devices. 51(12), pp. 2078-2085.

Nalbant, M., Gokkaya, H., Sur, G. 2007. Application of Taguchi Method in Optimization of Cutting Parameters for Surface Roughness Turning. International Journal Materials and Design. 28, pp. 1379-1385.

Nassif, S., Strojwas, A., Director, S. 1984. Fabrics ii: A Statistically Based IC Fabrication Process Simulator, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. 3, pp. 40-46.

Ninomiya, S. *et al.* 2009. V<sub>TH</sub> Control by Halo Implantation using the Sen's Mind System. International Workshop on Junction Technology. pp. 100-103.

Phadke, M. S. 1998. Quality Engineering Using Robust Design. Pearson Education, Inc. and Dorling Kindersley Publishing, Inc.

Salehuddin, F., Kaharudin, K. E., Elgomati, A, Ahmad, I., Apte, P. R., Nopiah, Z. M., Zaharim, A. 2013. Comparison of 2k-Factorial and Taguchi Method for Optimization Approach in 32nm NMOS Device. Mathematical Methods and Optimization Techniques in Engineering. pp. 125-134.

Salehuddin, F., Kaharudin, K. E., Zain, A. S. M., Mat Yamin, A. K., Ahmad, I. 2014. Analysis of Process Parameter Effect on DIBL in n-channel MOSFET Device using L27 Orthogonal Array. AIP Conferences Proceedings. 322, pp. 322-328.

Sylvester, D., Argawal, K., Shah, S. 2008. Variability in nanometer CMOS: Impact, Analysis and Minimization. Integration, the VLSI Journal. 41, pp. 319-339.

Taur, Y., Ning, T. H. 1998. Fundamental of Modern VLSI Devices. New York: Cambridge Univ. Press.

Wang, L. L., Liu, J., Guo, B., Zhao, Z. 2005. Precision Control of Halo Implantation for Scaling-down ULSI Manufacturing. Proc. IEEE International Symposium on Semiconductor Manufacturing. pp. 204-207.