## ARPN Journal of Engineering and Applied Sciences ©2006-2016 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

# ELECTRICAL CHARACTERIZATION OF DIFFERENT HIGH-K DIELECTRICS WITH TUNGSTEN SILICIDE IN VERTICAL DOUBLE GATE NMOS STRUCTURE

K. E. Kaharudin<sup>1</sup>, F. Salehuddin<sup>1</sup>, N. Soin<sup>2</sup>, A. S. M. Zain<sup>1</sup>, M. N. I. A. Aziz<sup>1</sup> and I. Ahmad<sup>3</sup>

<sup>1</sup>Micro and Nanoelectronics Research Group, Centre for Telecommunication Research and Innovation (CeTRI), Universiti Teknikal Malaysia Melaka (UTeM), Durian Tunggal, Melaka, Malaysia

<sup>2</sup>Department of Electrical Engineering, University of Malaya, Kuala Lumpur, Malaysia

<sup>3</sup>Centre for Micro and Nano Engineering (CeMNE), College of Engineering, Universiti Tenaga Nasional (UNITEN), Kajang, Selangor, Malaysia

E-Mail: khairilezwan@yahoo.com.my

#### ABSTRACT

The limitation of Poly-Si/ SiO<sub>2</sub> devices in producing a greater value of drive current (I<sub>ON</sub>) has become a major issue, especially for very small scale devices. It is believed that the problem may be resolved by introducing metalgate/high-*k* dielectrics to replace traditional Poly-Si/SiO<sub>2</sub> technology. This paper presents the performance analysis of several different high-*k* dielectrics technology with tungsten silicide (WSi<sub>x</sub>) as a metal-gate in ultrathin pillar vertical double-gate (DG) NMOS architecture. The device was virtually fabricated by using an ATHENA module of Silvaco TCAD tools. At the same time, the device characterization was carried out using an ATLAS module of Silvaco TCAD tools. The dielectric materials used for the simulation are known as Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, TiO<sub>2</sub> and ZrO<sub>2</sub>. Analysis of the results revealed that the WSi<sub>x</sub>/TiO<sub>2</sub> device has superior electrical characteristics compared to others. The significant improvement was observed in terms of the drive current (I<sub>ON</sub>) where the WSi<sub>x</sub>/TiO<sub>2</sub> device produced 2.845.2 μA/μm at 0.205 V of threshold voltage (V<sub>TH</sub>). This I<sub>ON</sub> value exceeds the minimum requirement predicted by the International Technology Roadmap Semiconductor (ITRS) 2013 for high performance (HP) multi-gate (MG) technology.

**Keywords:** drive current, high-k, metal-gate, NMOS.

#### 1. INTRODUCTION

The performance of metal-oxide-semiconductor field effect transistor (MOSFET) incorporating high-k dielectric significantly improves channel transport performance. It is difficult to apply traditional Poly-Si/SiO<sub>2</sub> technology to ultra-small gate length MOSFET especially to meet the requirements of high performance (HP) logic technology, which requires a very high drive current ( $I_{\rm ON}$ ) specification [1]. The small dimension of a Poly-Si/SiO<sub>2</sub>-based MOSFET has difficulty producing a drive current ( $I_{\rm ON}$ ) exceeding 1,480  $\mu$ A/ $\mu$ m as predicted by the International Technology Roadmap 2013 [1].

The smaller MOSFET device requires an increased capacitance gate dielectric to control the short channel effects such as hot carrier degradation [2, 3]. This can be achieved by modifying several device designs and reducing the gate oxide thickness (EOT). However, the reduction of EOT leads to the increased gate leakage which eventually decreases the drive current (I<sub>ON</sub>) [4]. For a thickness below 2 nm, the leakage is unacceptably high when SiO<sub>2</sub> is used as the gate dielectric material [5]. Therefore, the high-k dielectrics have been widely used as a gate dielectric material to replace the SiO<sub>2</sub> in current MOSFET's technologies due to their high dielectric constants [6, 7]. The dielectric layers with higher electrical permittivity are used in thicker films to reduce the leakage current and improve upon the reliability of the gate dielectric layer with electrical thickness equal to an ultrathin SiO<sub>2</sub> layer [8].

In this regard, Titanium dioxide (TiO<sub>2</sub>) has been extensively studied because of its remarkable optical and

electrical properties. Studies on thin films of TiO<sub>2</sub> have reported dielectric constants ranging from 40 to 86 [9]. The TiO<sub>2</sub> dielectric has the highest dielectric permitivitty compared to SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub> and ZrO<sub>2</sub>. Several reports on the TiO<sub>2</sub> effects towards the device characteristics of a single metal-gate MOSFET have been done by Afifah Maheran et al. The type of metal-gate used in their work is Tungsten Silicide (WSi<sub>x</sub>). The compatibility of a single WSix gate with the TiO2 dielectric was reported to result in a nominal V<sub>TH</sub> value (0.306 V) and a low leakage current (0.258 nA/µm) that satisfy the requirements of ITRS 2011 for a bulk single-gate device [10, 11]. Another report has proven that the combination of a single WSix gate with TiO<sub>2</sub> dielectrics have allowed the reduction of the gate length (Lg) from 32 nm to 22 nm while keeping the nominal V<sub>TH</sub> value [13]. The application of WSi<sub>x</sub> as a metal-gate is due to its compatibility with both NMOS and PMOS devices via metal-gate workfunction engineering proposed by Hong et al. patent [14].

Furthemore, Rahul *et al.* reported that the integration of Hafnium dioxide (HfO<sub>2</sub>) with the Nickel (Ni) as the metal-gate in Junctionless Vertical Double-gate MOSFET yielded a very high drive current ( $I_{ON}$ ) value of 1772  $\mu$ A/ $\mu$ m [14]. Their approach was based on varying the work function of the metal-gate in order to set the appropriate threshold voltage ( $V_{TH}$ ) of the device [14]. Therefore, a significant attempt to find the correct work function of the metal-gate is very crucial in order to stabilize the threshold voltage ( $V_{TH}$ ) [8]. The compatibility of different high-k dielectric materials with a metal-gate may differ due to their different dielectric constants [14].

In this paper, the electrical characteristics for the WSix integrated with  $Al_2O_3$  (k~9),  $HfO_2$  (k~25),  $TiO_2$  (k~85),  $ZrO_2$  (k~22)and Poly-Si/Si $O_2$  (k~3.9) are compared and analyzed utilizing Silvaco TCAD, ATHENA and ATLAS modules. The electrical performances of all the high-k materials with WSix gate in the vertical double-gate NMOS structure are investigated and presented in the following section.

#### 2. PROCESS SIMULATIONS

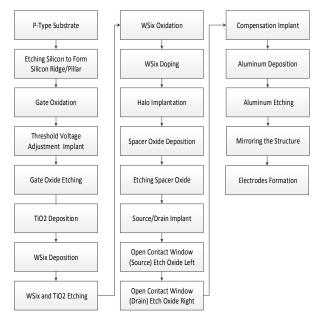

The key feature of the device fabrication method is depicted in Figure-1. A P-type silicon with <100> orientation was used as the main substrate for the device's design. The silicon substrate was doped with boron by a concentration of 1 x  $10^{14}$  atom/cm³. The doping with donors and acceptors was implemented in order to modify the electron and hole concentration in the silicon substrate within a very large range of  $10^{13}$  up to  $10^{21}$  [15]. The virtual process was followed by the gate oxidation process in which the silicon substrate was oxidized in dry oxygen for a short period of time.

**Figure-1.** Vertical double gate NMOS with WSix/TiO<sub>2</sub>Stack Technology process flowchart.

The next process was to etch the gate oxide in order to replace it with a thin layer of dielectric material. For instance, the titanium dioxide ( $TiO_2$ ) was selected as a dielectric material. The thickness of the  $TiO_2$  dielectric was approximately 3 nm. Therefore the equivalent oxide thickness (EOT) of the dielectric can be computed by using (1) [14]:

$$EOT = \left[\frac{\varepsilon_{SiO2}}{\varepsilon_{high-k}}\right] T_{high-K}(1)$$

Where  $\mathcal{E}_{SiO2}$  is the permittivity of SiO<sub>2</sub> which is 3.9,  $\mathcal{E}_{high-k}$  is the permittivity of high-k which is TiO<sub>2</sub> (85) and is the high-k dielectric physical thickness. Since the T<sub>high-k</sub> is approximately 3 nm, the EOT of the dielectric will be 0.138 nm. The gate oxide material with a dielectric constant (k) higher than SiO<sub>2</sub> will result in a smaller EOT even with a physical thickness (T<sub>high-k</sub>) larger than the SiO<sub>2</sub> (T<sub>ox</sub>).

The tungsten silicide (WSi<sub>x</sub>) was then deposited at the top of TiO<sub>2</sub> layer. Both TiO<sub>2</sub> and WSi<sub>x</sub> layers were etched to form the vertical gate. The work function of 4.5 eV was set for the WSi<sub>x</sub> gate [16]. After that, halo implantation was implemented in order to mitigate the short channel effects in MOSFET devices [17–19]. The sidewall spacers were then deposited in order to separate the two high dopant areas. It also acts as a diffusion buffer for the dopant atom in the source/drain that will cause the interception between the source / drain and gate when the distance is too close.

Since the device was a n-type, the source/drain implantation was done by implanting arsenic dosage as a n-type dopant. The compensation implantation was utilized later by implanting phosphor dosage. This process was performed to reduce parasitic capacitance that might slow down the device, thus deteriorating the device's performance. The top of the structure was then placed in contact with aluminum metal. The aluminum layer was deposited on the top structure's surface and any unwanted aluminum was etched to develop the contacts [20, 21].

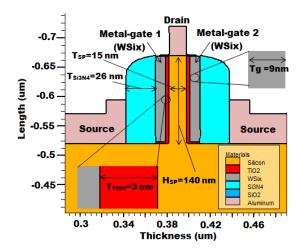

Next, metallization and etching were performed to form electrodes at the drain and source regions. The completed structure of the vertical double gate NMOS device with metal-gate/high-*k* stack technology was completed by mirroring the right-hand side structure. The completed structure of the Vertical Double Gate NMOS device with WSi<sub>x</sub>/TiO<sub>2</sub> stack technology is illustrated as in Figure-2. The process parameters that were used in the process simulation is summarized in Table-1.

**Figure-2.**Final structure of vertical double gate NMOS device with WSi<sub>x</sub>/TiO<sub>2</sub> Stack Technology.

### ARPN Journal of Engineering and Applied Sciences

© 2006-2016 Asian Research Publishing Network (ARPN). All rights reserved

#### www.arpnjournals.com

**Table-1.** Process parameters of vertical double gate NMOS device.

| Process parameters             | Units                                       | S WSix/Al <sub>2</sub> O <sub>3</sub> WSix/HfO <sub>2</sub> |      | WSix/TiO <sub>2</sub> | WSi/ZrO <sub>2</sub> |  |

|--------------------------------|---------------------------------------------|-------------------------------------------------------------|------|-----------------------|----------------------|--|

| Substrate Implant Dose         | atom cm <sup>-3</sup> (x10 <sup>-14</sup> ) | 1                                                           | 1    | 1                     | 1                    |  |

| V <sub>TH</sub> Implant Dose   | atom cm <sup>-3</sup> $(x10^{-12})$         | 1.81                                                        | 1.81 | 1.81                  | 1.81                 |  |

| V <sub>TH</sub> Implant Energy | kev                                         | 20                                                          | 20   | 20                    | 20                   |  |

| V <sub>TH</sub> Implant Tilt   | degree                                      | 10                                                          | 10   | 10                    | 10                   |  |

| Halo Implant Dose              | atom cm <sup>-3</sup> (x10 <sup>-12</sup> ) | 3.86                                                        | 5.47 | 2.82                  | 5.23                 |  |

| Halo Implant Energy            | kev                                         | 170                                                         | 170  | 170                   | 170                  |  |

| Halo Implant Tilt              | degree                                      | 28                                                          | 28   | 28                    | 28                   |  |

| S/D Implant Dose               | atom cm <sup>-3</sup> (x10 <sup>-18</sup> ) | 1.25                                                        | 1.25 | 1.25                  | 1.25                 |  |

| S/D Implant Energy             | kev                                         | 20                                                          | 20   | 20                    | 20                   |  |

| S/D Implant Tilt               | degree                                      | 80                                                          | 80   | 80                    | 80                   |  |

| Compensation Implant Dose      | atom cm <sup>-3</sup> (10 <sup>-12</sup> )  | 2.51                                                        | 2.51 | 2.51                  | 2.51                 |  |

| Compensation Implant<br>Energy | kev                                         | 60                                                          | 62   | 60                    | 60                   |  |

| Compensation Implant Tilt      | degree                                      | 7                                                           | 7    | 7                     | 7                    |  |

#### 3. DEVICE CHARACTERIZATION

Once the devices were built with ATHENA module, the completed devices were characterized by utilizing ATLAS module to provide characteristics such as the I<sub>D</sub> versus V<sub>GS</sub> curve. Device characteristics such as threshold voltage (V<sub>TH</sub>), drive current (I<sub>ON</sub>), off-leakage current (I<sub>OFF</sub>), I<sub>ON</sub>/I<sub>OFF</sub> ratio,

subthreshold swing (SS) and drain induced barrier lowering (DIBL) were retrieved from the simulation. The simulation results for the WSix-based gate with different high-k dielectric materials and poly-Si/SiO<sub>2</sub> channel devices were then compared and investigated. The device simulation setup condition is listed in Table-2 [22].

**Table-2.** Device simulation conditions [22].

| D                                     | Duain waltaga V (V)               | Gate voltage, V <sub>G</sub> (V) |                   |                      |  |

|---------------------------------------|-----------------------------------|----------------------------------|-------------------|----------------------|--|

| Device characteristics                | Drain voltage, V <sub>D</sub> (V) | V <sub>Initial</sub>             | V <sub>Step</sub> | $\mathbf{V}_{Final}$ |  |

| Threshold Voltage (V <sub>TH</sub> )  | 1.0                               | 0                                | 0.1               | 2.0                  |  |

| Drive Current (I <sub>ON</sub> )      | 1.0                               | 0                                | 0.1               | 2.0                  |  |

| Leakage Current (I <sub>OFF</sub> )   | 1.0                               | 0                                | 0.1               | 2.0                  |  |

| Subthreshold Swing (SS)               | 1.0                               | 0                                | 0.1               | 2.0                  |  |

| Drain Induced Barrier Lowering (DIBL) | 0.1                               | 0                                | 0.1               | 1.5                  |  |

|                                       | 3.0                               | 0                                | 0.1               | 1.5                  |  |

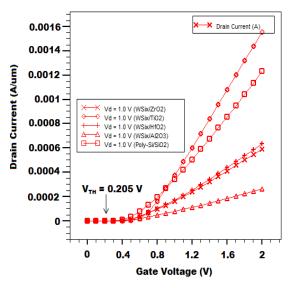

It is important to ensure that all the devices are set to the same level of V<sub>TH</sub> during the simulation. This was 0.205 V as predicted by ITRS 2013 for high performance (HP) multi-gate technology in the year 2020. This was done to precisely evaluate device performance in terms of the corresponding I<sub>ON</sub>, I<sub>OFF</sub>, I<sub>ON</sub>/I<sub>OFF</sub> ratio, SS and DIBL.

#### 4. RESULTS AND DISCUSSIONS

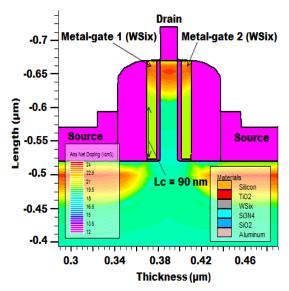

The device characteristics of both WSi<sub>x</sub>/TiO<sub>2</sub> and Poly-Si/SiO<sub>2</sub> Vertical Double-gate NMOS devices were extracted by utilizing ATLAS module. Figure-3 depicts the contour mode of vertical double gate NMOS device that shows the device's doping profile. The channel length

(Lc) between the source and the drain region was measured to be 90 nm approximately.

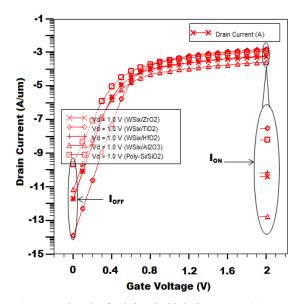

Figure-4 shows the graph of drain current (I<sub>D</sub>) versus gate voltage  $(V_G)$  at drain voltage  $V_D = 1.0 \text{ V}$  for Vertical Double-gate NMOS device with different high-k dielectric materials such as Al<sub>2</sub>O<sub>3</sub> (k~9), HfO<sub>2</sub> (k~25),  $TiO_2$  (k~85),  $ZrO_2$  (k~22) and  $Poly-Si/SiO_2$  (k~3.9). The threshold voltage (V<sub>TH</sub>) value for the device was fixed at 0.205 V.

Figure-5 depicts the graph of subthreshold drain current  $(I_D)$  versus gate voltage  $(V_G)$  at drain voltage  $V_D =$ 1.0 V for vertical double gate NMOS device. The value of leakage current (I<sub>OFF</sub>), drive current (I<sub>ON</sub>) and subthreshold swing (SS) was extracted from the graph. The I<sub>ON</sub> is the maximum drain current ( $I_{Dmax}$ ) when  $V_{GS}=V_{DD}$  and

$V_{DS}$ = $V_{DD}$ [23]. Meanwhile, the off-leakage current ( $I_{OFF}$ ) defined as a drain to source current and was measured when  $V_{GS}$ =0 and  $V_{DS}$ =  $V_{DD}$  [24]. In other words, the off-state current ( $I_{OFF}$ ) is the drain current when no gate voltage is applied.

**Figure-3.** Contour mode of vertical double gate NMOS device with WSi<sub>x</sub>/TiO<sub>2</sub> Stack Technology.

**Figure-4.** Graph of drain current (I<sub>D</sub>) versus gate voltage (V<sub>G</sub>).

The model equations for both the  $I_{ON}/I_{Dsat}$  and  $I_{OFF}$  are stated in (2) and (3) [25,26]:

$$I_{Dsat} = \frac{W}{L} \mu C_{inv} \frac{(V_{GS} - V_{TH})^2}{2}$$

(2)

where W is the effective channel width, L is the effective channel length,  $\mu$  is the carrier mobility in the channel (assumed constant here),  $C_{inv}$  is the gate capacitance density with channel in inversion,  $V_{GS}$  is the gate to source voltages, and  $V_{DS}$  is the drain to source voltages, and  $V_{TH}$  is the threshold voltage.

$$I_{OFF}(V_{GS}, V_{DS}) = I_{O}e^{(V_{GS} - V_{TH})/nV_{T}} (1 - e^{-V_{DS}/V_{T}})$$

(3)

where

$$I_o = \mu_o C_{ox} \frac{W}{L} V_T^2$$

,  $V_T = kT/q = 26mV$  is the

thermal voltage,  $C_{ox}$  is the oxide capacitance,  $\mu o$  is the zero bias mobility, W/L is the width over length ratio of the device, and n is the subthreshold swing coefficient.

Figure-5. Graph of subthreshold drain current ( $I_D$ )-gate voltage ( $V_G$ ).

The subthreshold swing (SS) value was obtained from the inverse slope of  $\log_{10} I_D \text{ vs. V}_{GS}$  characteristic. It shows how much change in the gate voltage is required to change the drain current by one decade as shown in (4) [27]:

$$SS = \left[\frac{d(\log_{10} I_{DS})}{dV_{GS}}\right]^{-1} \tag{4}$$

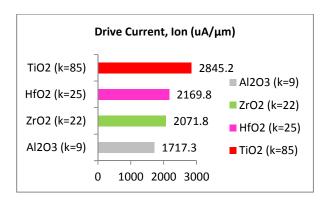

Table-3 shows the results of the device characteristics for the Poly-Si/SiO<sub>2</sub> based device and the WSi<sub>x</sub> with Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, TiO<sub>2</sub> and ZrO<sub>2</sub> based device. Based on Table-3, it is observed that the WSi<sub>x</sub>/TiO<sub>2</sub> device has produced the highest value of drive current (I<sub>ON</sub>) which is 2845.2  $\mu$ A/ $\mu$ m. In fact, all the device characteristics of the WSi<sub>x</sub>/TiO<sub>2</sub> based device were observed to be better than the others.

**Table-3.** Results of device characteristics for different technologies of vertical double gate NMOS devices.

| Device characteristics                                      | PolySi/SiO <sub>2</sub> | WSix/Al <sub>3</sub> O <sub>2</sub> | WSix/HfO <sub>2</sub> | WSix/TiO <sub>2</sub> | WSix/ZrO <sub>2</sub> |  |

|-------------------------------------------------------------|-------------------------|-------------------------------------|-----------------------|-----------------------|-----------------------|--|

| $I_{ON}(\mu A/\mu m)$                                       | 1231.9                  | 1717.3                              | 2169.8                | 2845.2                | 2071.8                |  |

| $I_{OFF}(pA/\mu m)$                                         | 225.4                   | 0.480                               | 0.002                 | 0.088                 | 0.002                 |  |

| I <sub>ON</sub> /I <sub>OFF</sub> ratio (x10 <sup>9</sup> ) | 0.006                   | 3.575                               | 1108                  | 0.323                 | 1020                  |  |

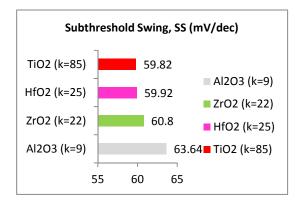

| SS (mV/dec)                                                 | 75.38                   | 63.64                               | 59.92                 | 59.82                 | 60.80                 |  |

| DIBL (mV/V)                                                 | 23.64                   | 28.16                               | 19.41                 | 1.817                 | 20.84                 |  |

Figure-6 depicts the effect of different high-k dielectric materials upon the  $I_{\rm ON}$  value of vertical double-gate NMOS device. It can be observed that the  $I_{\rm ON}$  is proportional to the permittivity of high-k dielectric materials. There is a significant improvement of the  $I_{\rm ON}$  value when  $TiO_2$  is used as a gate dielectric. This is due to a decrease in depletion as there is less boron penetration when a higher permittivity of high-k dielectric is applied [28]. The  $I_{\rm ON}$  is one of the important characteristic that determines the drive capability of the device [23].

Figure-6. I<sub>ON</sub> Values for different High-k dielectrics.

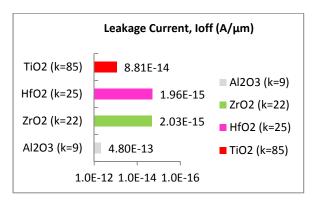

Figure-7 shows the effect of different high-k dielectric materials towards the I<sub>OFF</sub> value of the vertical double-gate NMOS device. Ideally, the I<sub>OFF</sub> value will be zero when no voltage is applied to the gate and the V<sub>DS</sub> is set equal to V<sub>DD</sub> (voltage supply) [23]. A higher dielectric constant material is introduced to replace SiO2 which allows a thicker dielectric to be deposited to reduce leakage without electrical thickness penalties [29, 30]. As a result, the thicker high-k dielectric gate will increase the overall capacitance, hence, decreasing the leakage current  $(I_{OFF})$ . It is important to ensure that the  $I_{OFF}$  is kept as minimal as possible in order to reduce the power consumption of the device [23]. It can be observed that the I<sub>OFF</sub> value value was at the lowest level when the HfO<sub>2</sub> (hafnium dioxide) dielectric is applied as the insulator of the WSi<sub>x</sub> (tungsten silicide) gate.

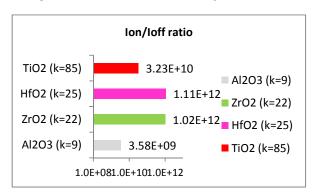

The  $I_{\rm ON}/I_{\rm OFF}$  ratio is the important characteristic that indicates the ratio of total  $I_{\rm ON}$  to the  $I_{\rm OFF}$ . The  $I_{\rm ON}/I_{\rm OFF}$  ratio represents the power consumption of a device. The higher the  $I_{\rm ON}/I_{\rm OFF}$  ratio, the better will be the power consumption of the device. From Figure-8, the highest  $I_{\rm ON}/I_{\rm OFF}$  ratio recorded is produced by WSi<sub>x</sub>/HfO<sub>2</sub> device,

which indicates that the combination of  $WSi_x$ -gate with the  $HfO_2$  dielectric demonstrates a better power consumption than the other devices.

**Figure-7.** I<sub>ON</sub> Values for different High-*k* dielectrics.

**Figure-8.**  $I_{ON}/I_{OFF}$  ratio for different High-k dielectrics.

The subthreshold swing (SS) is an important characteristic in MOSFET's device that indicates the speed of the switching transition from "ON" to "OFF" state, or vice versa [27]. The lower SS value, the faster will be the switching operation. It also indicates how effectively the flow of drain current can be halted when  $V_{GS}$  is decreased below  $V_{TH}$ . In this regard, Figure-9 exhibits the decrease of the SS value when a higher dielectric constant of high-k material is applied as the WSix gate insulator.

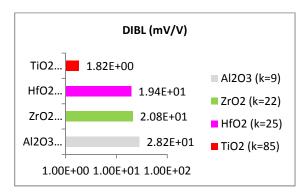

The drain induced barrier lowering (DIBL) is a type of short channel effect in MOSFETs. It refers to a reduction of  $V_{TH}$  at higher drain voltage ( $V_D$ ). The DIBL effect occurs in short channel devices when the depletion region of the drain and the source interact with each other.

This interaction turns on the device prematurely [31]. In other words, DIBL is defined as the ratio of change in threshold voltage,  $\Delta V_{TH}$  to the change in drain voltage  $\Delta V_D$ . To measure the DIBL value, two values of threshold voltage,  $V_{TH1}$  and  $V_{TH2}$  must be extracted at  $V_{D1}$ =0.1 V and  $V_{D2}$ =3.0 V. The value of DIBL is computed by using (5) [32]:

$$DIBL = \frac{V_{TH1} - V_{TH2}}{V_{D2} - V_{D1}}$$

(5)

**Figure-9.** SS values for different High-*k* dielectrics.

Figure-10 shows the effects of different high-*k* dielectric towards the DIBL value in vertical double-gate NMOS device. It can be observed that the DIBL value of vertical double WSi<sub>x</sub>-based gate NMOS device can be suppressed by using a higher dielectric constant of high-*k* materials. Based on all the experimental results, it can be concluded that the vertical double WSi<sub>x</sub>-based gate NMOS device is more compatible with the TiO<sub>2</sub> due to its superior device characteristics, especially the I<sub>ON</sub> value that meets the requirement of high performance (HP) multi-gate (MG) technology predicted by International Technology roadmap Semiconductor (ITRS) 2013 (ITRS 2013).

**Figure-10.** DIBL values for different High-*k* dielectrics.

Table-4 shows the comparison of observed device characteristics for the WSi<sub>x</sub>/TiO<sub>2</sub> vertical double gate NMOS device with other researchers. There are a few improvements on the overall device characteristrics of the simulated device compared to the results obtained from previous works. The I<sub>ON</sub> value of the WSi<sub>x</sub>/TiO<sub>2</sub> vertical double gate NMOS device is slightly lower than the result obtained by Rahul *et al.* [13]. This might be due to the different types of material, channel length (Lc) and workfunction of the metal-gate [8,13].

However, the  $I_{ON}$  value of this recent work still exceeds 1,480  $\mu$ A/ $\mu$ m predicted by ITRS 2013 [1]. The DIBL value of the device is the lowest among others due to its long channel length (Lc) and the presence of nitride barrier (Si<sub>3</sub>N<sub>4</sub>) that can reduce the possibility of charge sharing effect between the source and the drain region. The channel length (Lc) can be controlled by varying the height of the silicon pillar [21,33]. Alternatively, the channel length (Lc) can also be controlled by varying the source and the drain implant tilt angle [34]. The vertical double gate MOSFET structure developed by Kim *et al.* produced a very low SS value compared to the others due to the hetero-junction and the selective epitaxial growth (SEG) technique [35].

| <b>Table-4.</b> Benchmark of vertical double | gate NMOS devices through simulation. |

|----------------------------------------------|---------------------------------------|

|                                              |                                       |

| Author                   | Device<br>technology     | Channel<br>length<br>(nm) | Ion<br>(μA/μm) | Ioff<br>(pA/μm) | Ion/Ioff<br>ratio (x10 <sup>9</sup> ) | SS<br>(mV/dec) | DIBL<br>(mV/V) |

|--------------------------|--------------------------|---------------------------|----------------|-----------------|---------------------------------------|----------------|----------------|

| Saad et al. (2008) [34]  | Poly-Si/SiO <sub>2</sub> | 90                        | 200            | 0.00001         | 20,000                                | 100            | 94             |

| Saad et al. (2010) [36]  | Poly-Si/SiO <sub>2</sub> | 50                        | 588            | 0.0552          | 10.65                                 | 81.9           | 62             |

| Rahul et al. (2014) [13] | Poly-Si/SiO <sub>2</sub> | N/A                       | 720            | 113.4           | 0.006349                              | 63.74          | 44.29          |

| Rahul et al. (2014) [13] | Nickel/HfO <sub>2</sub>  | N/A                       | 1772           | 1422            | 0.001246                              | 61.01          | 40.4           |

| Kim et al. (2015) [35]   | TiN/SiO <sub>2</sub>     | N/A                       | 100            | N/A             | N/A                                   | 32             | N/A            |

| From this work           | Poly-Si/SiO <sub>2</sub> | 90                        | 1231.9         | 225.4           | 0.006                                 | 75.38          | 23.64          |

| From this work           | WSix/TiO <sub>2</sub>    | 90                        | 2845.2         | 0.088           | 0.323                                 | 59.82          | 18.17          |

## ARPN Journal of Engineering and Applied Sciences © 2006-2016 Asian Research Publishing Network (ARPN). All rights reserved.

#### www.arpnjournals.com

#### 5. CONCLUSIONS

In conclusion, the WSi<sub>x</sub>/TiO<sub>2</sub> stack technology has been virtually integrated with the vertical double-gate NMOS device. Based on the simulation results using SILVACO TCAD tools, the TiO2 has been recognized as the most suitable high-k dielectric material for vertical WSix-based double-gate NMOS device due to its excellent device characteristics that meets the requirement of high performance (HP) multi-gate (MG) technology predicted by ITRS 2013. In the present investigation, the major difference between WSi<sub>x</sub>/TiO<sub>2</sub> device with the others was in terms of the drive current (I<sub>ON</sub>) value. The drive current (I<sub>ON</sub>) of WSi<sub>x</sub>/TiO<sub>2</sub> device exceeded the minimum value which is 1,480 μA/μm as specified in ITRS 2013. The presence of both WSix and TiO2 dielectric enormously increased the channel capacity of the device. The rapid mobility of ion movement in the channel tremendously increased the drive current (IoN). Moreover, the WSix/TiO2 device demonstrated excellent power consumption due to its higher I<sub>ON</sub>/I<sub>OFF</sub> ratio.

#### **ACKNOWLEDGEMENT**

The authors would like to thank to the Ministry of Higher Education (MOHE), MyBrain15, UM CR 004-2013 fund and the Centre for Telecommunication Research and Innovation (CeTRI), Faculty of Electronics and Computer Engineering (FKEKK), Universiti Teknikal Malaysia Melaka (UTeM), for sponsoring this research study under the research grants (PJP/2014/FKEKK(6B)/S01341).

#### REFERENCES

- [1] ITRS 2013 Report, International Technology Roadmap Semiconductor, 2013. http://www.itrs.net.

- [2] N. M. Karim, N. Soin, S. Manzoor, F.Y. Soon, M. Mounir. 2013. Prediction of energy change due to hot carrier injection in nano- structured CMOS system: perspective of an envelope detector. Microelectron. Eng. 111: 256-260.

- [3] S. Shahabuddin, N. Soin, K.K. Goh, Y.A. Wahab, H. Hussin. 2013. Voltage Dependences of Parameter Drifts in Hot Carrier Degradation for n- channel LDMOS Transistors. Microelectron. Eng. 109: 101-104.

- [4] Y.A. Wahab, N. Soin, S.W.M. Hatta. 2014. Defects evolution involving interface dispersion approaches in high-k/metal-gate deep-submicron CMOS. Microelectron. Reliab. pp. 2234-2338.

- [5] N. Atan, I. Ahmad, B.Y. Majlis, I.A. Fauzi. 2014. Effects of High-k Dielectric with Metal Gate for Electrical Characteristics of Nanostructured NMOS. Math. Methods Eng. Econ. 1: 111-115.

- [6] H. Hussin, N. Soin, M.F. Bukhori, S.W.M. Hatta, Y.A. Wahab. 2014. Effects of Gate Stack Structural and Process Defectivity on High-k Dielectric Dependence of NBTI Reliability in 32 nm Technology Node PMOSFETs. Sci. World J. pp.1-13.

- [7] S.W.M. Hatta, Z. Ji, J.F. Zhang, W.D. Zhang, N. Soin, B. Kaczer *et al.* 2014. Energy distribution of positive charges in high-k dielectric. Microelectron. Reliab. 54: 2329-2333.

- [8] N.M. Idris, A. Brown, J. Watling, A. Asenov. 2010. Simulation Study of Workfunction Variability in MOSFETs with Polycrystalline Metal Gate. Ultim. Integr. Silicon. pp. 165-168.

- [9] S. Duenasl, H. Castanl, H.Garcial, E.S. Andres, M. Toledano-Luque, I. Martil, et al. 2005. A comparative study of the electrical properties of TiO<sub>2</sub> Film grown by high-pressure reactive sputtering and atomic layer deposition. Inst. Phys. Publ. Semicond. Sci. Technol. 20: 1044-1051.

- [10] A.H. Afifah Maheran, P.S. Menon, I. Ahmad, S. Shaari. 2014. Optimisation of Process Parameters for Lower Leakage Current in 22 nm n-type MOSFET Device using Taguchi Method. J. Teknol. 68: 1-5.

- [11] A.H. Afifah Maheran, I. Ahmad, S. Shaari, H.A. Elgomati. 2014. 22nm NMOS device with lowest leakage current optimized using Taguchi Method. Commun. Circuits Educ. Technol. pp. 170-173.

- [12] A.H. Afifah Maheran, P.S. Menon, I. Ahmad, S. Shaari, H.A. Elgomati, F. Salehuddin. 2013. Design and Optimization of 22 nm Gate Length High-k/Metal gate NMOS Transistor. J. Phys. Conf. Ser. 431: 1-9.

- [13] J. Rahul, S. Yadav, V.K. Bohat. 2014. Effects of Metal Gate Electrode and HfO<sub>2</sub> in Junction less Vertical Double Gate MOSFET. Int. J. Sci. Eng. Technol. 3(5): 671-674.

- [14] Z. Hong, A. Bodkhe, S. Tzeng. 2014. Method for Forming A Low Resistivity Tungsten Silicide Layer for Metal Gate Stack Applications. http://www.google.com/patents/US20140363942.

- [15] Z.Y. Zhao, D. Hendrix, L.Y. Wu, B.K. Cusson. 2003. Ion Implantation Angle Variation to Device Performance and the Control in Production. AIP Conf. Proc. pp. 666-669.

## ARPN Journal of Engineering and Applied Sciences ©2006-2016 Asian Research Publishing Network (ARPN). All rights reserved.

#### www.arpnjournals.com

- [16] F. Ana, Najeeb-ud-din, Gate Workfunction Engineering for Deep Sub-Micron MOSFET's: Motivation, Features and Challenges. Int. J. Electron. AndCommunication Technol. 2: 29-35.

- [17] A. Erlebach, T. Feudel, A. Schenk, C. Zechner. 2004. Influence of HALO and drain-extension doping gradients on transistor performance. Mater. Sci. Eng. B Solid-State Mater. Adv. Technol. pp. 114-115.

- [18] V.N. Faifer, D.K. Schroder, M.I. Current, T. Clarysse, P.J. Timans, T. Zangerle, et al. 2007. Influence of halo implant on leakage current and sheet resistance of ultrashallow p-n junctions. J. Vac. Sci. Technol. B Microelectron. Nanom. Struct. 25: 1588-1592.

- [19] F. Salehuddin, I. Ahmad, F.A. Hamid, A. Zaharim 2011. Impact of Different Dose and Angle in HALO Structure for 45nm NMOS Device, Adv. Mater. Res. 383-390: 6827-6833.

- [20] K.E. Kaharudin, F. Salehuddin, A.H. Hamidon, A.S.M. Zain, M.N.I.A. Aziz, I. Ahmad. 2016. Variability Analysis of Process Parameters on Subthreshold Swing in Vertical DG-MOSFET Device. ARPN Journal of Engineering and Applied Sciences. 11(5): 3137-3142.

- [21] K.E. Kaharudin, F. Salehuddin, A.S.M. Zain, M.N.I.A. Aziz. 2016. Optimization of process parameter variations on leakage current in in siliconon-insulator vertical double gate MOSFET device. ARPN Journal of Engineering and Applied Sciences. 11(6): 3838-3848.

- [22] SILVACO. 2006. Silvaco ATLAS manual Device Simulation Software. http://ridl.cfd.rit.edu/products/manuals/Silvaco/atlas\_users.pdf.

- [23] V.K. Yadav, A.K. Rana. 2012. Impact of Channel Doping on DG-MOSFET Parameters in Nano Regime-TCAD Simulation. Int. J. Comput. Appl. 37: 36-41.

- [24] F. Salehuddin, I. Ahmad, F.A. Hamid, A. Zaharim. 2009. Application of Taguchi Method in Optimization of Gate Oxide and Silicide Thickness. Int. J. Eng. Technol. 9: 94-98.

- [25] S.M. Sze. 1981. Semiconductor Devices: Physics and Technology, 2<sup>nd</sup> Ed, John Wiley and Son Inc., N.Y.

- [26] D. A. Buchanan. 1999. Scaling the gate dielectric: Material, Intergaration and Reliability. IBM J. Res. Dev. 43: 245-264.

- [27] Ferain, C.A. Colinge, J. Colinge. 2011. Multigate Transistors as the Future of Classical Metal-oxidesemiconductor Field-effect Transistors. Nature. 479: 310-316.

- [28] Dun-Bao Ruan, K.-S. Chang-Liao, C.-C. Li, C.-C. Lu, Y.-L. Liao, L.-T. Chen, et al. 2015. Improved electrical characteristics of high-k gated MOSFETs with post-growth treatment on interfacial layer, Microelectron. Eng. 138: 81-84.

- [29] R. Chau, S. Datta, M. Doczy, B. Doyle, J. Kavalieros, M. Metz. 2004. High-k/metal-gate stack and its MOSFET characteristics. IEEE Electron Device Lett. 25: 408-410.

- [30] R. Chau, J. Brask, S. Datta, G. Dewey, M. Doczy, B. Doyle, et al. 2005. Application of high-k gate dielectrics and metal gate electrodes to enable silicon and non-silicon logic nanotechnology. Microelectron. Eng. 80: 1-6.

- [31] S. Farhana, A. Z. Alam, S. Khan. 2015. DIBL and Subthreshold Swing Effect on Carbon Nanotube Field Effect Transistor, in: Proc. World Congr. Eng. 4-7.

- [32] F. Salehuddin, K.E. Kaharudin, A.S.M. Zain, A.K.M. Yamin, I. Ahmad. 2014. Analysis of process parameter effect on DIBL in n-channel MOSFET device using L27 orthogonal array. Int. Conf. Fundam. Appl. Sci. AIP Conf. Proc. 322-328.

- [33] M. A. Riyadi, I. Saad, R. Ismail. 2010. Investigation of pillar thickness variation effect on oblique rotating implantation (ORI)-based vertical double gate MOSFET. Microelectronics J. 41: 827-833.

- [34] Saad, R. Ismail. 2008. Self-aligned vertical double-gate MOSFET (VDGM) with the oblique rotating ion implantation (ORI) method. Microelectronics J. 39: 1538-1541.

- [35] H. W. Kim, B.-G. Park, J. H. Kim, S. W. Kim. 2015. Vertical type double gate tunnelling FETs with thin tunnel barrier. Electron. Lett. 51: 718-720.

- [36] Saad, M.A. Riyadi, F. M. N. Zul Atfyi, A. M. A. Hamid, R. Ismail. 2010. Enhanced performance of vertical double gate MOSFET (VDGM) with oblique rotating implantation (ORI) method. IEEE Int. Conf. Semicond. Electron. Proceedings, ICSE. pp. 175-179.