# ARPN Journal of Engineering and Applied Sciences

© 2006-2016 Asian Research Publishing Network (ARPN). All rights reserved

www.arpnjournals.com

## IMPACT OF DIFFERENT GROUND PLANES OF UTBB SOI MOSFETS ON DIGITAL AND ANALOG FOM

Noraini Othman<sup>1</sup>, M. K. Md Arshad<sup>1,2</sup>, S. N. Sabki<sup>1</sup> and U. Hashim<sup>1,2</sup> <sup>1</sup>School of Microelectronic Engineering, UluPauh, Perlis, Malaysia <sup>2</sup>Institute of Nano Electronic Engineering, Universiti Malaysia Perlis, UluPauh, Perlis, Malaysia E-Mail: noraini othman@unimap.edu.my

#### ABSTRACT

In this work, we investigate the impact of different ground plane (GP) structures of the ultra-thin body and buried oxide SOI MOSFETs (UTBB SOI MOSETs) on the digital and analog figures-of-merits (FoM) with gate length of L<sub>e</sub>= 25 nm and 10 nm. Different GP structures are found to have significant impact on the drain-induced barrier lowering (DIBL) while the impact on subthreshold-slope (SS) is negligible. Incorporation of localized ground plane of p-type in the substrate underneath the channel (referred herein as GP-B structure) provides excellent results of DIBL as of the incorporation of n+/p+/n+ structure underneath the buried-oxide (referred herein as GP-C structure). The effective suppression of the substrate depletion effect is observed with showing no increase in the potential under the channel for both GP-B and GP-C structures between low (V<sub>d</sub>=20 mV) and high (V<sub>d</sub>=1 V) drain bias. However, as the simulations were extended to analog FoM, it is found that only GP-B structure managed to maintain excellent result in terms of voltage gain, A<sub>v</sub> while GP-C showed deteriorations due to an early increase in output conductance, g<sub>d</sub>at low frequency.

Keywords: UTBB SOI MOSFETs, ground planes, digital and analog figures-of-merit.

#### INTRODUCTION

In Ultra-Thin Body and BOX (UTBB), the reduction of BOX thickness reduces the lateral electrostatic coupling between the source and drain, which allows for better control of short channel effects (SCEs) (Burignat et al., 2010; Liu et al., 2010; Xu et al., 2012). However, when the BOX is very thin, a depleted zone can extend into the underlying substrate, which causes the BOX to behave as a thick-BOX due to an increase in the BOX equivalent thickness. In order to counter this effect, implementations of ground plane (GP) doping has been introduced to limit the field penetration under the BOX from propagating to the source (Wong et al., 1999; Ernst et al., 2002). The GP can be achieved with incorporations of heavily doped substrate (Wong et al., 1998; Fenouillet-Beranger et al., 2009; Yan et al., 2010; Fenouillet-Beranger et al., 2011; Fenouillet-Beranger et al., 2010). With GP, the reduction of DIBL in the order of ~50 mV has been reported (Fenouillet-Beranger et al., 2009; Fenouillet-Beranger et al., 2010) which are the results of suppression of the depletion layer under the BOX (Kumar et al., 2008; Arshad et al., 2012). The incorporation of GP also allows for modulation of the threshold voltage if a ground plane contact is added for back-biasing (Wong et al., 1998; Fenouillet-Beranger et al., 2010; Grenouillet et al., 2012; Tsuchiya et al., 2004). In this work, we investigate and compare the impact of different ground planes of UTBB SOI MOSFETs. This is to determine which GP structures can effectively eliminate substrate depletion effects and produce the best digital and analog performance.

#### SIMULATION METHODS

#### Simulation methodology

The simulations were carried out using Sentaurus Device simulator. The physics models used include the hydrodynamic transport model, Lombardi mobility model and Shockley-Read-Hall recombination model.In this work, the density gradient model is used to evaluate the influence of quantization effects The gate length used in the simulations were of 25 nm and 10 nm in order to observe the changes in the short-channel behaviour. Graphs of drain current versus gate voltage (I<sub>d</sub>-V<sub>g</sub>) were plotted at V<sub>d</sub>=20 mV and 1.0 V. We verify the simulated results of I<sub>d</sub>-V<sub>g</sub> for device with std-GP at L<sub>g</sub>=25 nm are comparable with experimental results as in Burignat et al., 2010 and Liu et al., 2010.

#### Simulated device structure

The simulations started off with a no-ground plane (no-GP) UTBB SOI MOSFET structure with V<sub>d</sub>of 20 mV and 1 V. Gate voltage (Vg) is swept from 0 to 1.5 V in 10 mV incremental steps. The buried oxide (BOX) and Sibody thickness are 10 nm and 7 nm respectively. The channel was undoped with acceptor concentration of 6.5x10<sup>14</sup> cm<sup>-3</sup> while S/D donor concentrations doping are of 1x10<sup>20</sup> cm<sup>-3</sup>. Metal gate work function of 4.65 eV and an effective oxide thickness (EOT) of 1.2 nm were used.Detailed reviews on advanced silicon-on-insulator MOSFETs can be found in Arshad et al., 2015.

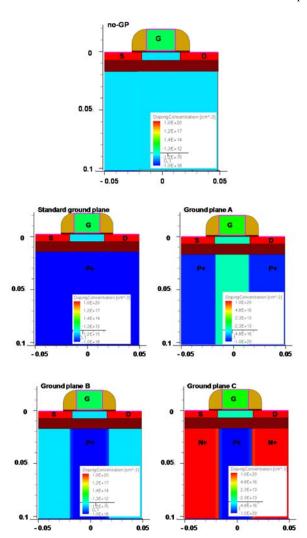

We made comparison of the no-GP structure with several ground plane structures as illustrated in Figure-1 i.e. standard ground plane (std-GP), ground plane A (GP-A), ground plane B (GP-B) and ground plane C (GP-C).

www.arpnjournals.com

**Figure-1.** Different ground plane structures of UTBB SOI MOSFETs: no-GP,standard ground plane (std-GP), ground-plane A (GP-A), ground-plane B (GP-B) and ground-plane C (GP-C).

The std-GP structure employed a thin layer of P+ doping of 1x10<sup>18</sup> cm<sup>-3</sup> under the BOX region. For GP-A structure, P+ doping of 1x10<sup>20</sup> cm<sup>3</sup> were created under the S/D area, which are similar to Makiyama et al., 2012. InGP-B structure, P+ doping of 1x10<sup>18</sup> cm<sup>3</sup> was formed under the channel. The last structure of GP-C simulated N+ doping of 1x10<sup>20</sup> cm<sup>-3</sup> under the S/D area while area under the channel was P+ doped with 1x10<sup>20</sup> cm<sup>-3</sup>. This structure was similar to Yan et al., 2010. All these structures can be done in a self-aligned manner: the formation of localized highlydoped regions in the substrate underneath the BOX both has been demonstrated theoretically experimentally(Xiong & Colinge, 1999)(Xiong et al., 2002). We then extend our analysis by reducing the gate length from the initial 25 nm down to 10 nm to observe the changes in the short-channel behavior

#### RESULTS AND DISCUSSIONS

#### **DIGITAL FIGURES-OF-MERIT**

#### Drain-induced barrier lowering, DIBL

DIBL is caused by the encroachment of the depletion region from the drain into the channel due to high drain bias (V<sub>d</sub>), which in turn causes the lowering of the potential energy barrier for electrons in the channel. As a result, drain current, (I<sub>d</sub>) increases and the threshold condition can be reached at a lower gate voltage (Vg) since the drain has already created a large portion of the depletion region. Strong DIBL is an indication of poor short-channel behavior as it implies that the gate no longer has total control over the channel. The strength of the DIBL is usually measured as the difference in V<sub>th</sub> between a low V<sub>d</sub> (i.e.  $V_d$ =20-100 mV) and a high  $V_d$  (i.e.  $V_d$ =1 V).In this work, DIBLis extracted as (V<sub>thlin</sub>-V<sub>thsat</sub>)/ΔV<sub>d</sub>(Colinge & Colinge, 2002) at drain current, I<sub>d</sub> of 10<sup>-7</sup> A for two drain voltages i.e. V<sub>d</sub>=20 mV and V<sub>d</sub>=1.0 V. This method is widely used and seems to be the most suitable method to extract DIBL.

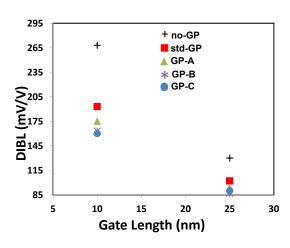

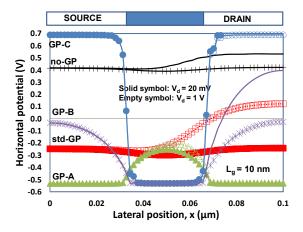

Figure-2 shows the DIBL extracted at two different gate lengths i.e. L<sub>g</sub>=25 and 10 nm. As expected, when the gate length is reduced, DIBL is also increased. At L<sub>g</sub>=10 nm, both GP-B and GP-C showed comparable results with both seemed to exhibit the lowest DIBL as compared with other GPs.In order to explain the superiority of GP-B and GP-C structures and to investigate substrate depletion effects, we take a look at the horizontal potential (2 Horizontal) distribution at 1 nm under the substrate/BOX interface from the source through the channel and end at the drain as shown in Figure-3 for 10 nm gate length. As reported in Othman et al., 2014, the simulated DIBL curves translate into different space-charge conditions at the substrate/BOX interface. DIBL is a function of gate voltage that is highly dependent on  $\mathbb{Z}_F$  whereby  $(V_{th}=V_{fb}+2\mathbb{Z}_F+(|Q_d|/C_{ox}))$ . At the substrate/BOX interface, the surface potential referred to quasi-neutral substrate, i.e.  $\mathbb{Z}_s = \mathbb{Z}_{Horizontal} - (V_{sub} - \mathbb{Z}_F)$  where 2 F here is the Fermi level equals to 276 mV which allows for examining the potential rise due to drain bias in terms of the obtained operating regime, i.e.  $\mathbb{Z}_s$  <0 indicates accumulation,  $0 < \mathbb{Z}_s < 0.53 \text{ V}$  indicates depletion and  $\mathbb{Z}_s > 0.53 \text{ V}$ 0.53 V indicates strong inversion. One can see that:

- In the channel, GP-B and GP-C are in accumulation, whereas standard-GP and GP-A are in depletion while no-GP is in inversion. For GP-B, the depletion region terminate within the S/D boundary under the BOX, without extending into the channel region (unlike of std-GP).

- ii. When the drain bias is increased from  $V_d$ =20 mV to  $V_d$ =1.0 V, the potential remain the same i.e. there is no increase of potential under the channel region for GP-B and GP-C. This shows that both GPs provide better shield to the channel from the influence of drain electric field when a high drain voltage is applied. This benefit translates into the low DIBL value as illustrated in Figure-2 for 10 nm gate length.

#### www.arpnjournals.com

Figure-2. Results of DIBL as a function of gate length, L<sub>g</sub>.

Figure-3. Horizontal potential along the substrate/BOX interface at linear ( $V_d$ =20 mV) and at saturation ( $V_d$ =1 V) for  $L_g$ =10 nm.

#### Subthreshold slope, SSlin

Next, we look into the subthresholdslope, since GP structures normally yield higher body factor than no-GP due to suppression of depletion effect (Arshad et al., 2013). S-slope can be defined as the change in gate bias  $(V_g)$ required to change the subthreshold drain current (I<sub>d</sub>) by one decade as given by SS=ΔV<sub>g</sub>/ΔlogI<sub>d</sub>. In other words, it indicates how effective the flow of drain current of a device can be stopped when Vg is decreased below Vth. Low Sslope is desirable as it indicates faster transition of the transistors from OFF to ON state. Table-I shows that higher S-slopewere obtained when the gate length is being reduced. It can be seen that GP structures showed better Sslope than no-GP. However, the improvements of S-slope with different GPs are quite small in overall (only between 3mV/dec-8mV/dec improvements). Although GP-B and GP-C are highly doped underneath the channel, they did not degrade the S-slope. This shows that both structures provide greater capacitive coupling between gate and channel, hence a better control of the gate over the channel potential(Numata et al., 2002; Numata and Takagi, 2004).

**Table-1.** Linear subthreshold slope (mV/dec) versus gate length.

|        | L <sub>g</sub> =25 nm | L <sub>g</sub> =10 nm |

|--------|-----------------------|-----------------------|

| No-GP  | 89                    | 112                   |

| Std-GP | 79                    | 96                    |

| GP-A   | 87                    | 95                    |

| GP-B   | 79                    | 93                    |

| GP-C   | 79                    | 94                    |

#### Analog figures-of-merit

From digital, we extend our investigation to figures-of-merit. Ingeneral, the amplifying performance of analog transistors deteriorates with increasing frequency. In Makovejev, 2012, it is reported that the analogue performance degradation caused by the substrate effects are stronger than self-heating for UTBB devices with 7-8 nm Si body and 10 nm BOX. Moreover, the effect of parasitic elements whose impact on the device performance increases enormously in deeply downscaled devices can also be seen in the evaluations of a widefrequency band (Kilchytska et al., 2014; Arshad et al., 2014). In this work, we look into different perspective i.e. the analogue performance of the different GP structures with L<sub>g</sub>=10 nm evaluated for frequency range from 0.01 Hz to  $1x10^{14}$ Hz. The evaluations are made on the results of the transconductance (g<sub>m</sub>), output conductance (g<sub>d</sub>) and intrinsic gain (A<sub>v</sub>).

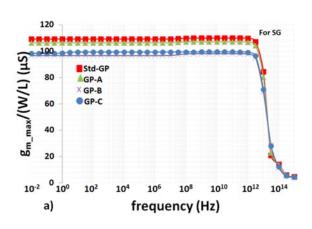

#### Small-signal transconductance, gm

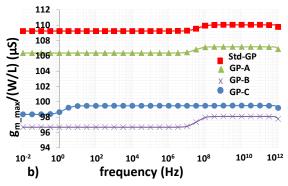

In small-signal analysis,  $g_m$  as a function of frequency is determined from the Y-parameter,  $g_m=|Y_{21}-Y_{12}|$  where  $Y_{21}$  is the forward transconductance and  $Y_{12}$  is the reverse transconductance. The maximum transconductance was normalized to the gate width and length and is given by:  $g_{m\_max\_norm}=g_{m\_max}/(W/L)$ . From Figure-4(a), it can be seen that different GP structures only give minor impacts on the results of  $g_{m\_max\_norm}$ . This can be seen from Figure-4(b) that reveals GP-C structure showing a slight increase of  $g_{m\_max\_norm}$  at a much lower frequency in contrast with its other 3 GP counterparts. However, the  $g_{m\_max\_norm}$  differences between the GP structures can still be considered very small i.e. ~12  $\mu$ S.

#### www.arpnjournals.com

**Figure-4.** (a)  $g_{m\_max}/(W/L)$  as a function of frequency.  $L_g$ =10 nm, W=1  $\mu m$  and  $V_d$ =1 V. (b) Emphasizing slight differences of  $g_{m\_max}/(W/L)$  between the different GP structures as a function of frequency.

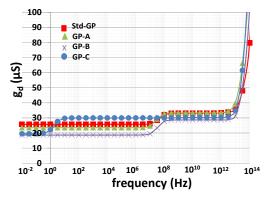

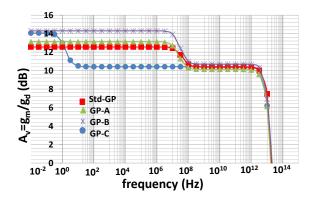

### Intrinsic gain, Av

The amplification factor, also called gain, is the extent to which an active device boosts the strength of a signal. Variation of voltage gain is denoted as A<sub>v</sub>=g<sub>m</sub>/g<sub>d</sub> where  $g_m = |Y_{21} - Y_{12}|$  and  $g_d = Y_{22}$ . Figure-5 shows the results of the corresponding  $g_d$  (refer to Figure-4 for the  $g_{m max}$ ). It can be seen that with an increase in frequency, gdalso increases. Different GPs are translated into gd increase at different frequency level with GP-C is the first one to increase. From Figure-6, different GP structures were found to have only minor impacts on the maximum  $A_v$  that varies from 12 dB to 14 dB, due to a more pronounced effect of gdon A<sub>v</sub> as compared to g<sub>m</sub>. This is evident where it is noted that the gain for GP-C started to drop at a very low frequency which correspond to an increase in g<sub>d</sub> as shown in Figure-5. The same trend is also observed for std-GP, GP-A and GP-B. In overall, GP-B which showed the best DIBL among its GP peers in the digital analysis, managed to maintain good A<sub>v</sub> results in terms of the highest maximum A<sub>v</sub> and a stable gain up to 10 MHz frequency.

Figure-5. Simulated  $g_d$  as a function of frequency for SG .L<sub>g</sub>=10 nm, W=1  $\mu$ m.

**Figure-6.** Intrinsic gain, A<sub>v</sub> as a function of frequency.L<sub>g</sub>=10 nm, and V<sub>d</sub>=1 V.

#### CONCLUSIONS

In this work, implications of different ground plane (GP) structures on the digital and analogFoM were evaluated. It is found that the introduction of p+ doping under the channel as in GP-B and GP-C structures enable potential pinning in the channel area, resulting in no increase in the potential under the channel between low (V<sub>d</sub>=20 mV) and high (V<sub>d</sub>=1 V) drain bias. Meanwhile, in the analogFoM, the different GPs seemed to give impacts on the voltage gain, A<sub>v</sub> (degradation at different frequency) as a result of different gd increase across the frequency range. It is found that as the simulations were extended to analogFoM, only GP-B structure managed to maintain excellent result in terms of voltage gain, Av while GP-C showed deteriorations due to an early increase in output conductance, g<sub>d</sub>at low frequency. Overall, the application of GP is dependent on the device application i.e. digital or analogFoM.

## REFERENCES

Arshad, M.K., Raskin, J-P., Kilchytska, V., Andrieu, F., Scheiblin, P., Faynot, O. and Flandre, D. 2012. Extended Master Modeling of DIBL in UTB and UTBB SOI MOSFETs. IEEE Transactions on Electron Devices, pp. 247–251.

# ARPN Journal of Engineering and Applied Sciences © 2006-2016 Asian Research Publishing Network (ARPN). All rights reserved.

#### www.arpnjournals.com

Arshad, M.K., Makovejev, S., Olsen, S., Andrieu, F., Raskin, J-P., Flandre, D. and Kilchytska, V. 2013. UTBB SOI MOSFETs analog figures of merit: Effects of ground plane and asymmetric double-gate regime. Solid-State Electronics, 90, pp.56–64.

Arshad, M.K., Kilchytska, V., Emam, M., Andrieu, F., Flandre, D. and Raskin, J-P. 2014. Effect of parasitic elements on UTBB FD SOI MOSFETs RF Figure of Merit. Solid-State Electronics, 97, pp. 38-44.

Arshad, M.K., Othman, N. and Hashim, U. (2015) Fully Depletion of Advanced Silicon on Insulator MOSFETs. Critical Reviews in Solid State and Materials Sciences, 40(3), pp.182-198

Burignat, S., Flandre, D., Arshad, M.K., Kilchytska, V., Andrieu, F., Faynot, O. and Raskin, J-P. 2010. Substrate impact on threshold voltage and subthreshold slope of sub-32nm ultra thin SOI MOSFETs with thin buried oxide and undoped channel. Solid-State Electronics, 54(2), pp. 213-219.

Colinge, J.-P. and Colinge, C.-A. 2002. Physics of Semiconductor Devices, New York: Kluwer Academic Publishers.

Ernst, T., Tinella, C., Raynaud, C. and Cristoloveanu, S. 2002. Fringing fields in sub-0.1 um fully depleted SOI MOSFETs: optimization of the device architecture. Solid-State Electronics, 46, pp. 373-378.

Fenouillet-Beranger, C., Denorme, S., Perreau, P., Buj, C., Faynot, O., Andrieu, F. *et al.* 2009. FDSOI devices with thin BOX and ground plane integration for 32nm node and below. Solid-State Electronics, 53(7), pp.730-734.

Fenouillet-Beranger, C., Perreau, P., Denorme, S., Tosti, L., Andrieu, F., Weber, O. *et al.* 2010. Impact of a 10nm ultrathin BOX (UTBOX) and ground plane on FDSOI devices for 32nm node and below. Solid-State Electronics, 54(9), pp. 849-854.

Fenouillet-Beranger, C., Thomas, O., Perreau, P., Noel, J.-P., Bajolet, A., Haendler, S. *et al.* 2010. Efficient Multi-VT FDSOI technology with UTBOX for low power circuit design. Symposium on VLSI Technology Digest of Technical Papers. pp. 65-66.

Fenouillet-Beranger, C., Perreau, P., Tosti, L., Thomas, O., Noel, J.-P., Benoist, T. *et al.* 2011. Low power UTBOX and Back Plane (BP) FDSOI technology for 32nm node and below. IEEE Intl. Conference on IC Design & Technology (ICICDT).

Grenouillet, L., Vinet, M., Gimbert, J., Giraud, B., Noel, J.-P., Liu, Q. *et al.* 2012. UTBB FDSOI transistors with dual STI for a multi-V t strategy at 20nm node and below. IEDM. pp. 64-67.

Kilchytska, V., Makovejev, S., Arshad, M.K., Raskin, J-P. and Flandre, D. 2014. Perspective of UTBB FD SOI MOSFETs for Analog and RF Applications. Functional Nanomaterials and Devices for Electronics, Sensors and Energy Harvesting. Springer International Publishing, pp. 27-47.

Kumar, M.J. and Siva, M. 2008. The Ground Plane in Buried Oxide for Controlling Short-Channel Effects in Nanoscale SOI MOSFETs. IEEE Transactions on Electron Devices, 55(6), pp. 1554-1557.

Liu, Q., Yagishita, A., Loubet, N., Khakifirooz, A., Kulkarni, P., Yamamoto, T. *et al.* 2010. Ultra-Thin-Body and BOX (UTBB) Fully Depleted (FD) Device Integration for 22nm Node and Beyond. 2010 Symposium on VLSI Technology Digest of Technical Papers. pp. 61-62.

Makiyama, H., Yamamoto, Y., Tsunomura, T., Iwamatsu, T., Sonoda, K., Oda, H., Sugii, N. and Yamaguchi, Y. 2012. Novel Local Ground-Plane Silicon on Thin BOX (SOTB) for Improving Short-Channel-Effect Immunity. Euro SOI. pp. 27–28.

Makovejev, S. 2012. Characterisation of Thermal and Coupling Effects in Advanced Silicon MOSFETs. Newcastle University.

Numata, T., Uchida, K., Koga, J. and Takagi, S.-I. 2002. Device Design for Subthreshold Slope and Threshold Voltage Control in sub-100 nm Fully-Depleted SOI MOSFETs. 2002 IEEE International SOI Conference, pp.179-180.

Numata, T. and Takagi, S.-I. 2004. Device design for subthreshold slope and threshold voltage control in sub-100-nm fully depleted SOI MOSFETs. IEEE Trans. Electron Devices, 51(12), pp. 2161-2167.

Othman, N., Arshad, M.K. and Hashim, U. 2014. Lower DIBL in Inverted Substrate of UTBB SOI n-MOSFETs. IEEE International Conference on Semiconductor Electronics (ICSE) 2014. pp. 76-79.

Tsuchiya, R., Horiuchi, M., Kimura, S., Yamaoka, M., Kawahara, T., Maegawa, S., Ipposhi, T., Ohji, Y. and Matsuoka, H. 2004. Silicon on Thin BOX: A New Paradigm of the CMOSFET for low power and High-Performance Application Featuring Wide-Range Back-Bias Control. IEDM Technical Digest. pp. 631–634.

Wong, H.P., Frank, D.-J. and Solomon, P.-M. 1998. Device Design Considerations for Double-Gate, Ground-Plane, and Single-Gated Ultra-Thin SO1 MOSFET's at the 25 nm Channel Length Generation. IEDM Technical Digest. pp. 407-410.

Wong, H.P., Frank, D-.J., Solomon, P-.M., Wann, C-.H.J. and Welser, J-.J. 1999. Nanoscale CMOS. Proc. of the IEEE. pp. 537-570.

# ARPN Journal of Engineering and Applied Sciences

© 2006-2016 Asian Research Publishing Network (ARPN). All rights reserved.

#### www.arpnjournals.com

Xiong, W. and Colinge, J.P. 1999. Self-aligned implanted ground-plane fully depleted SOI MOSFET. Electronic Letters, 35(23), pp. 2059-2060.

Xiong, W., Ramkumar, K., Jang, S.J., Park, J.-T. and Colinge, J.-P. 2002. Self-Aligned Ground-Plane FDSOI MOSFET. IEEE International SOI Conference, pp. 23-24.

Xu, N., Andrieu, F., Ho, B., Nguyen, B.Y., Weber, O., Mazure, C., Faynot, O., Poiroux, T. and Liu, T.J.K. 2012. Impact of back biasing on carrier transport in ultra-thinbody and BOX (UTBB) Fully Depleted SOI MOSFETs. 2012 Symposium on VLSI Technology (VLSIT). pp. 113-114.

Yan, R., Duane, R., Razavi, P., Afzalian, A., Ferain, I., Lee, C.W. et al. 2010. LDD and Back-Gate Engineering for Fully Depleted Planar SOI Transistors with Thin Buried Oxide. IEEE Transactions on Electron Devices, 57(6), pp. 1319-1326.