# ARPN Journal of Engineering and Applied Sciences

© 2006-2016 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

# LOW POWER CMOS CIRCUIT DESIGN FOR R WAVE DETECTION AND SHAPING IN ECG

D. Hari Priya<sup>1</sup>, A. S. C. S. Sastry<sup>1</sup> and K. S. Rao<sup>2</sup>

<sup>1</sup>K L University, Andhra Pradesh, India

<sup>2</sup>Department of Electronics and Communication Engineering, Anurag Group of Institutions, Hyderabad, India

E-Mail: <a href="mailto:haripriyaece@cvsr.ac.in">haripriyaece@cvsr.ac.in</a>

## ABSTRACT

R wave is an important morphological feature in ECG which plays a vital role in identifying Cardiac arrhythmias. A band pass filter is used to detect QRS complex which after rectification is shaped into a 200ms square pulse utilizing comparator circuit with auto threshold. This is implemented in 180nm technology and is simulated using Cadence Virtuoso. The circuit is tested with simulated ECG with heart beat ranging from 40 beats/min to 200 beats/min with an operating voltage of 0.4V and total power measured is  $3.997\mu W$ .

Keywords: cardiac arrhythmias, QRS complex, R-wave.

## 1. INTRODUCTION

QRS complex is detected as pulse to identify cardiac arrhythmias. The various morphological features and amplitude provide more information that helps the doctors to analyze and diagnose heart diseases. Apart from this several algorithms have been developed to detect the QRS complex accurately with offline data [1]. Algorithms for detecting ORS complex like nonlinear transformations using differentiation [2], a combination of differentiation, squaring and integration, a combination of differentiation and correlation, methods based on optimized and matched filtering, adaptive methods, wavelet transform, neural networks, combination of wavelet transform and neuralnetwork based adaptive filtering, and quite recently proposed methods based on mathematical morphology, voting algorithm, geometrical matching and modified pspectrum [3].

The properties of QRS complex like Slope, Amplitude and Width are considered and an algorithm is constructed by Pan Tompkins for real time applications [4]. A futuristic approach is introduced on simple moving average with wavelet based de-noising for real time detection. Most of the pre-recorded data is used to analyze the Cardiac Arrhythmias condition in real-time which is most essential to understand the practical requirements.

In practical patient monitoring and diagnostic system the heart rate variability(HRV), any abnormalities, classification arrhythmias has been inherently calculated in QRS detection methods based on software[5]. The QRS detector must be optimized for various conditions like high respiration, moving patient which are noise prevalent. But to design a system with above factors and to reduce the noise the Application Specific Integrated Circuit (ASIC) is required [6].

ASIC chips are designed using linear filtering and peak detection techniques to implement the QRS detection with threshold. Non-linear transformation and wavelet transform are also used to enhance the detection of QRS complex. Some of the QRS detectors reviewed in the literature have used wireless transmission [7]. Which are operated with supply voltage ranging from 2.5-3.3V

and consumes current of 30  $\mu A$  except transmitter. A QRS detector chip for wireless health monitoring system is developed with piezo-microphone sensor and a transmitter operating with 0.9V and consuming 7.5  $\mu A$ .

The programmable DSP HR for the ASIC model [8] is implemented in 1 µm CMOS technology with specified Supply voltage and Power consumption values. The wavelet transform technique is utilized in the chip implementation [9] which detects the peaks values by Dynamic Trans-linear circuit approach [10]. It has 5 Parallel scales and the reported power consumption is 55nW with the supply voltage of 2V which implemented in custom Bipolar IC design process. The design which is presented in another proposed model is developed and implemented in 0.13 µm technology with a supply voltage of 1.2V which includes the same transformation of wavelet and includes a wavelet transformation ratio threshold along with filter banks for wavelets [11] with the power consumption of 114 nW and 37.9 nW in alert and normal modes. The other demonstrated models comprise of filter banks and multi-scale multipliers is implemented in 0.18 µm technology with simulated power consumption of 644.9 nW when all the filters are active and 318.4 nW in normal operation [12]. When first half of the filters are active 90% of the power consumption is caused by deep submicron technology which has leakage issues. As a final point of cessation, among the many presented models in literature review, a very rare number of models have a supply voltage of below 1V.

The design approach is presented in Section II which introduces the principle operation of half wave rectifier, sample and hold circuit, Comparator and Monostable circuit. Section III reports the measurement results. The proposed work is concluded in Section IV.

#### 2. SYSTEM DESIGN

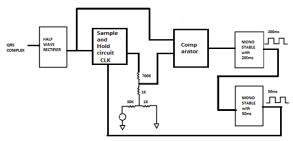

The block diagram of the system for detecting R-peak and shaping it into 200ms is in Figure.1. The ECG signal is filtered by band pass filter that allows only QRS complexes which was given input to the proposed system. The half wave rectifier removes the negative components

Q and S in the QRS complex and allows only R peak. The sample and hold circuit samples this R peaks which set an automatic threshold for the comparator when turned ON triggers a monoshot produces 200ms pulse. This in turn triggers a second monoshot to produce the pulse of 50ms duration to act as a sampling clock.

Figure-1. R peak detection and shaping circuit

#### Design of half wave rectifier

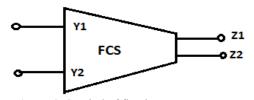

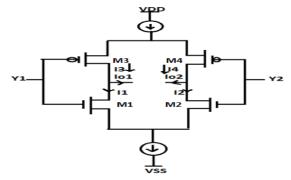

A low power half wave rectifier is designed using floating current source and four complementary MOS transistors M1, M2, M3 and M4 which are connected as two differential pairs as M1-M2 and M3-M4 are assumed to match and operate in the saturation region. The symbol and circuit is shown in Figures.2 & 3. The output current generated from circuit is balanced to gratifying the Kirchhoff's current law. The output current equations are given below.

$$I_{B2} = I_{B1} + I_{O1} + I_{O2}$$

(1)

$$I_{B2} = I_{B1} \tag{2}$$

$$I_{O1} = -I_{O2}$$

(3)

**Figure-2.** Symbol of floating current source.

**Figure-3.** CMOS Implementation of floating current source circuit.

The transconductance of M1 -  $M_2$  ( $g_{m1} = g_{m2}$ ) and  $M_3 - M_4$  ( $g_{m3} = g_{m4}$ ) are equal as they are assumed to equal transistors. The transconductance and output impedance of the FCS circuit is given in equation (2) & (3).

$$g_{mo1} = -g_{mo2} = (g_{m1} + g_{m3}) / 2$$

(4)

$$\begin{split} R_{o1} = R_{o2} &= \left[ \left( \left( \left( g_{m3} \, g_{ds3} \right) \, / \left( g_{m3} + g_{m4} \right) \right) + \left( \left( g_{ml} \, g_{ds1} \right) \, / \left( g_{ml} + g_{m2} \right) \right) \right]^{-1} \\ &= 2 / \left( g_{ds1} + g_{ds3} \right) \end{split} \tag{5}$$

Two balanced output currents are given by

$$I_{o1} = -I_{o2} = -1/2 \ V_d \left[ \sqrt{k_n} \sqrt{(I_{B1} - (k_n V_d^{2/4}))} \right] + \sqrt{k_p}$$

$$\sqrt{(I_{B1} - (k_p V_d^{2/4}))}$$

(6)

Where  $V_d = V_1 - V_2$

$V_1$  and  $V_2$  are voltages applied to  $Y_1$  and  $Y_2$  respectively  $K_n$  and  $K_p$  is the NMOS and PMOS transconductance parameters given by

$$K_n = \mu_n C_{ox} W_1 / L_1$$

(7)

$$K_p = \mu_p C_{ox} W_1 / L_1$$

(8)

Where

$\mu$  = mobility of carrier

$C_{ox}$  = gate capacitance per area

$W_1$ ,  $L_1$  = Channel width and channel length

of MOS transistor.

$I_{B1}$ ,  $I_{B2}$  = bias currents

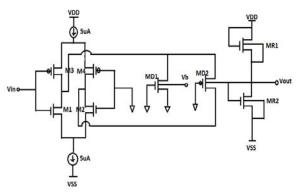

Half wave rectifier circuit consists of FCS, four diode and resistor. The folded current source circuit convert voltage source QRS complex into two current sources. The current source is rectifying by four diodes which are constructed by two transistors  $M_{\rm D1}$  and  $M_{\rm D2}$  and one pair of diode current is connected to ground as the rectification is half wave. The current output from diode is converted into voltage using  $M_{\rm R1}$  and MR2 CMOS transistor which are acted as resistor  $R_o$  in saturation region.  $D_1$  and  $D_2$  are initiated to ready for conduction by bias voltage  $V_b$  which is shown in Figure-4.

Figure-4. CMOS design of half wave rectifier.

The  $R_{\text{o}}$  and the relativity of the positive and negative polarity input voltage and output voltage are expressed as

$$K_p = \mu_p C_{ox} W_1 / L_1$$

(8)

Where  $V_{TH}$  is the threshold voltage and  $V_{GS}\!\!=\!\!V_{DD}\!\!=\!\!|V_{SS}|$   $V_{in}\!<\!0\ I_{out}\!=\!\text{-}(g_{m1}+g_{m3})\ Vin/2,\ V_{out}\!=\ I_{out}\ .\ R_o$

$$V_{in} > 0 I_{out} = (g_{m1} + g_{m3})V_{in}/2, V_{out} = I_{out} . R_o$$

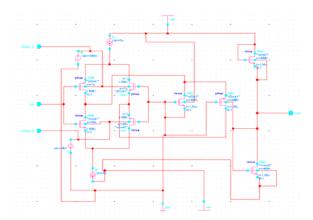

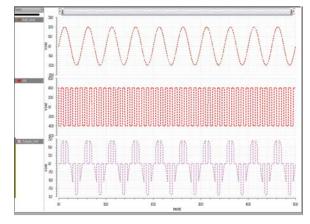

The schematic and simulation result of half wave rectifier in Cadence environment is given in Figure-5 & Figure-6.

Figure-5. CMOS design of half wave rectifier in cadence.

**Figure-6.** Simulation result of half wave rectifier in cadence environment.

# Design of sample and hold circuit

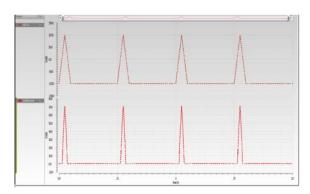

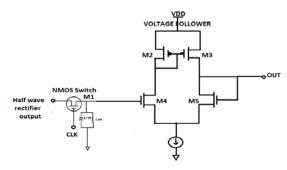

Sample & Hold Circuit is designed to sample the positive QRS complex with 50ms clock and to hold the sampled value for a short interval. The sample and hold circuit is shown in Figure-7. The sampling clock controls whether to sample the input signal or hold the last sampled value of QRS complex. When the pulse is high the signal is sampled and is low the signal value is holded. Thus the circuit has two modes of operation depending upon the logic level of clk signal. Upon receiving the input clock

pulse, the circuit samples the input and output follows input by voltage follower. The schematic and simulation result of sample hold circuit in Cadence environment is given in Figure-8 & Figure-9.

Figure-7. CMOS design of sample and hold circuit.

**Figure-8.** CMOS design of sample and hold circuit in cadence.

**Figure-9.** Simulation result of sample and hold circuit in cadence environment.

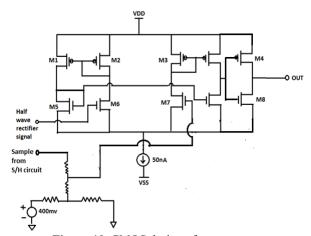

#### **Design of comparator**

The low power comparator is designed by using differential amplifier. It compares half wave rectifier output and with reference voltage. The reference voltage is generated by potential divider with samples from sample

and hold circuit. M2, M3 and M6, M7 transistors are differential pairs.

If

$$Vin = Vp - Vn < Vref Vout = -Vdd$$

If

$$Vin = Vp - Vn > Vref Vout = +Vdd$$

The half wave rectifier signal is less than Vref, the non-inverting input of the comparator is less than the inverting input. The output will be LOW at the negative supply voltage -Vdd resulting in a negative saturation of the output.

The half wave rectifier signal is greater than Vref, the non-inverting input of the comparator is greater than the inverting input. The output will be high at the positive supply voltage +Vdd resulting in a positive saturation of the output. Based on this comparator operation, the R-Peak is identified using suitable Vref. The value of Vref is set automatically based on QRS complex R-peak value using potential divider circuit. The CMOS comparator circuit is shown in Figure-10. The schematic and simulation in Cadence environment is given in Figure-11 & Figure-12.

Figure-10. CMOS design of comparator.

Figure-11. CMOS design of comparator in cadence.

**Figure-12.** Simulation result of comparator in cadence environment.

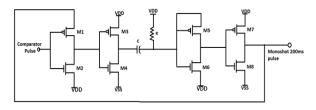

#### Design of monostable multivibrator

Monostable Multivibrators are designed to generate the refractory period of 200ms and to sample the QRS complex with 50ms sampling rate. It is triggered by comparator output pulse where the pulse is denoting the R-peak. Refractory time period is set by the time constant of the RC coupled circuit. The expression for time constant is given below

$$T = 0.69 RC$$

(6)

The monoshot circuit is given in Figure. If the Rpeak pulse trigger is low, the first NOR gate output is high. The resistor R is connected to the supply voltage. So the capacitor C has the same charge on both of its plates. The Junction of R and C voltage is equal and the second NOR gate output is low and the circuit is in "Stable State" with zero output. The R-peak pulse trigger is high, the first NOR gate output is low. So the capacitor C has logic 0 and start to discharge. The second NOR gate output is high and the circuit is in "Unstable State with an output voltage equal to +Vdd.

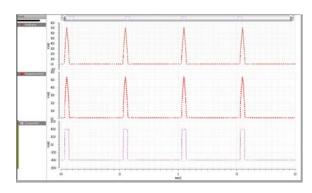

The second NOR gate maintain unstable state until the timing capacitor charging up through resistor, R reaches the minimum input threshold voltage of second NOR gate. This cause it to change state as logic level "1" value has appeared on its inputs. And change the output into logic "0" which in turn feedback to first NOR gate input. This action automatically returns the monostable back to its original stable state and awaiting a second trigger pulse to restart the timing process once again. The CMOS design of Mono stable circuit is shown in Figure-13. The schematic and simulation in Cadence environment of Mono shot circuit with 200ms width and Mono shot circuit with 50ms width is given in Figure-14, Figure-15, Figure-16 & Figure-17.

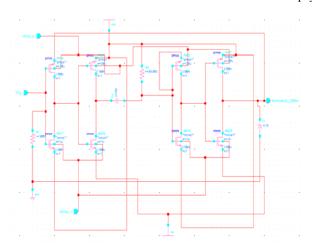

Figure-13. CMOS circuit design of mono shot circuit.

**Figure-14.** CMOS design of mono shot with 200ms width in cadence.

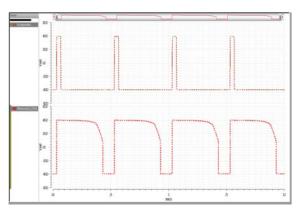

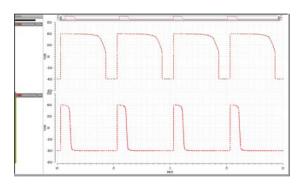

**Figure-15.** Simulation result of mono shot circuit with 200ms width in cadence environment.

**Figure-16.** CMOS design of mono shot with 50ms width in cadence.

**Figure-17.** Simulation result of mono shot circuit with 50ms width in cadence environment.

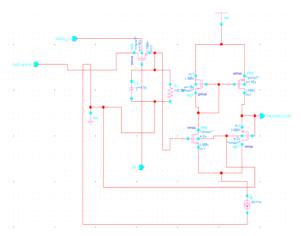

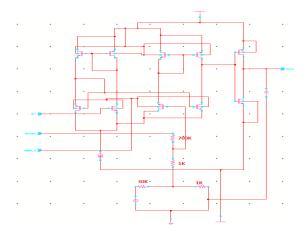

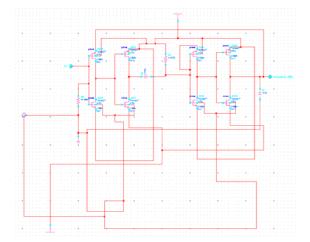

#### 3. MEASUREMENT RESULT

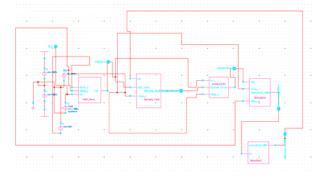

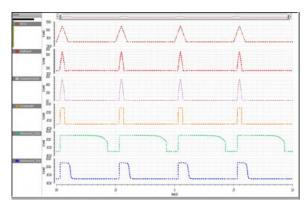

Detection of R- peak and shaping circuit is designed with low power and low voltage using body biasing technique. The overall circuit and simulation result is given in Figure-18 & Figure-19 This circuit is suitable for 40mv to 220mv voltage and 5Hz to 12.5 KHz frequency range. The operating voltage of circuit is  $\pm$  400mv with 3.99 $\mu$ W power consumption. The measurement result of the circuit is given in Table-1.

**Table-1.** Measurement result of QRS detection circuit.

| CIRCUIT                                    | PARAMETER         | MEASURED       |

|--------------------------------------------|-------------------|----------------|

|                                            | Ripple factor     | 2.11           |

|                                            | Form factor       | 2.337          |

| Half wave                                  | Peak Factor       | 3.814          |

| rectifier                                  | Efficiency        | 42.78%         |

|                                            | Offset voltage    | 11.468μV       |

| Comparator                                 | Offset Voltage    | 651.9897 μV    |

|                                            | Delay             | 3.298µs        |

|                                            | Rise time         | 96.34 µs       |

|                                            | Fall time         | 34.4 µs        |

| Monoshot circuit                           | Offset voltage    | 184.492nV      |

|                                            | Delay             | 130.8µs        |

|                                            | Rise time         | 123µs          |

|                                            | Fall time         | 504.59862μs    |

| R-Peak detection<br>and shaping<br>circuit | Operating voltage | <u>+</u> 400mv |

|                                            | Power consumption | 3.997µW        |

**Figure-18.** CMOS design of R peak detection and shaping circuit in cadence.

**Figure-19.** Simulation result of R-peak detection and shaping circuit in cadence environment.

#### 4. CONCLUSIONS

A low power and low voltage approach for detection of R- peak and shaping is presented and it is simulated in 180nm Technology Cadence environment. It had low power and energy efficient as per measured result. This circuit is tested for the ECG frequency ranging from 40 beats/min to 200 beats/min. The proposed circuit can be integrated with the amplifier and filtering circuitry to make a system on chip for identifying Cardiac arrhythmias.

# ACKNOWLEDGEMENTS

The authors express their gratitude to Dr. P. Rajeswar Reddy Chairman Anurag Group of Institutions for providing all the resources and facilities in carrying out this work. They are highly thankful to Prof. K.S.R. Krishna Prasad, NIT Warangal for his valuable suggestions and guidance. They also express thanks to Prof. J.V. Sharma H.O.D ECE Dept., friends and colleagues.

#### REFERENCES

- [1] Qiu P & Liu K J R (2008) A robust Method for QRS Detection Based on Modified pSpectrum, IEEE International Conference on Acoustics, Speech and Signal Processing: 501–504.

- [2] J. Pan and W. Tompkins. 1983. A real-time QRS detection algorithm. IEEE Transactions on Biomedical Engineering. BME-32(3): 230-236.

- [3] Köhler B-U, Hennig C & Orglmeister R (2002) The Principles of Software QRS Detection, IEEE Engineering in Medicine and Biology, 21(1): 42–57.

- [4] Liu X, Zheng Y J, Phyu M W, Zhao B, Je M & Yuan X J (2010) A Miniature OnChip Multi-Functional ECG Signal Processor with 30 μW Ultra-Low Power Low power Consumption, Proceedings of the 32<sup>nd</sup> 108 Annual International Conference of the IEEE

- Engineering in Medicine and Biology Society: 2577–2580.

- [5] Teo T H, Lim G K, David D S, Tan K H, Gopalakrishnan P K & Singh R (2007) Ultra Low-Power Sensor Node for Wireless Health Monitoring System, IEEE International Conference on Circuits and Systems: 2363–2366.

- [6] Chang M-C, Lin Z-X, Chang C-W, Chan H-L & Feng W-S (2004) Design of a System-on-Chip for ECG Signal Processing, The 2004 IEEE Asia-Pacific Conference on Circuits and Systems: 441–444.

- [7] Lahti J, Ruha A & Lappeteläinen M (1995) AProgrammable DSP ASIC for Heart Rate Measurement Applications, Proceedings of the European Solid-State Circuit Conference, 1: 158–161.

- [8] Haddad S A P, Houben R & Serdijn W A (2003) Analog Wavelet Transform Employing Dynamic Translinear Circuits for Cardiac Signal Characterization, Proceedings of the 2003 International Symposium on IEEE Circuits and Systems, 1:121–124.

- [9] Mulder J, Serdijn W A, van der Woerd A C & Roermund A H M (2000) Dynamic Translinear Circuits – An Overview, Analogue Integrated Circuits and Signal Processing, 22(2–3): 111–126.

- [10] Rodrigues J N, Öwall V & Sörnmo L (2004) A Wavelet Based R-Wave Detector for Cardiac Pacemakers in 0.35 CMOS Technology, Proceedings of the 2004 International Symposium on IEEE Circuits and Systems, 4: 13–16.

- [11] Hoang T-T, Son J-P, Kang Y-R, Kim C-R, Chung H-Y & Kim S-W (2006) A Low Complexity, Low Power, Programmable QRS Detector Based on Wavelet Transform for Implantable Pacemaker IC, IEEE International SOC Conference: 160–163.

- [12] Wong L S Y, Hossain S, Ta A, Edvinsson J, Rivas D H & Nääs H (2004) A Very Low-Power CMOS Mixed-Signal IC for Implantable Pacemaker Applications, IEEE Journal of Solid-State Circuits, 39(12): 2446–2456.

- [13] D. Hari Priya1, A. S. C. S. Sastry2 and K. S. Rao3 (2016) FPGA based design and implementation for detecting Cardiac arrhythmias, ARPN Journal of Engineering and Applied Sciences,vol.11,Issue.5,1819-6608.