# ARPN Journal of Engineering and Applied Sciences

© 2006-2017 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

# ENERGY EFFICIENT CONSUMPTION FOR QUALITY BASED SLEEP SCHEDULING IN WIRELESS SENSOR NETWORKS

A. S. Syed Navaz<sup>1</sup>, N. Asha<sup>2</sup> and D. Sumathi<sup>2</sup> <sup>1</sup>Department of Computer Applications, Muthayammal College of Arts and Science, Namakkal, Tamil Nadu, India <sup>2</sup>VIT University, Vellore, Tamil Nadu, India E-Mail: a.s.syednawaz@gmail.com

# ABSTRACT

This paper considers the problem of conserving energy in a single node in a wireless sensor network by turning off the node's radio for periods of a fixed time length. While packets may continue to arrive at the node's buffer during the sleep periods, the node cannot transmit them until it wakes up. The objective is to design sleep control laws that minimize the expected value of a cost function representing both energy consumption costs and holding costs for backlogged packets. Large number of very small size, low cost, low power multifunctional sensor nodes constitute the WSN. These sensors way the understanding of the physical world by sensing, processing and transmitting the data. The above functions are highly influenced by factors such as power, energy and lifetime of the sensor nodes. This technical paper explores various low power design architectures like reconfigurable hardware, sleep walker, variable dual VDD, modular architecture and folded tree architecture by presenting a comprehensive survey concerning passive and active power control mechanisms in WSN with investigation of the existing solution and evaluation.

Keywords: QoS, wireless sensor networks, SNOC, power consumption, FPGA, VDDL.

#### 1. INTRODUCTION

Wireless Sensor Networks (WSNs) hold the promise of many new applications in the area of environment surveillance and target tracking. In such applications, the user is interested only in the occurrence of a certain event, such as target appearances or status changes. Due to the random distribution or mobility of the targets, a certain level of sensing coverage over the field of interest should be maintained to guarantee that events of interest will be captured with minimal delay. The sensing area of a sensor node is often assumed to be a disk bound by a sensing circle of fixed radius r centred at the node. The field is said to be *k*-covered or have a coverage degree of k if any point contained in it is within the sensing area of at least k sensors [1]. In general, coverage degree can be considered as a measure of quality of service of a wireless sensor network [2]. The higher the coverage degree is, the better the field is monitored. However, the constrained power supply of sensors cannot justify the scheme in which all sensors are put on duty to achieve a high coverage degree. Continuous working leads to the quick depletion of battery power and this shortens the overall network lifetime. Moreover, sensors have limited processing ability and storage capacity due to low cost and small size. Therefore, power-efficient and lightweight designs to prolong network lifetime without sacrificing the coverage degree are one of the fundamental concerns for wireless sensor networks.

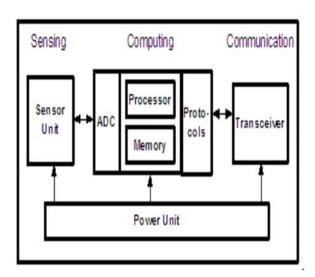

Wireless sensor networks are the widely used platform to interact with physical world. Low power WSN design allows the wireless sensor networks to be used in applications such as military, agriculture, biomedical, structural and environment monitoring [4]. The major components of the wireless sensor nodes are the sensor, radio and microcontroller unit along with the power supply using battery. But the radio transmission consumes more energy; they must be designed such that they consume minimum power so as to extend the lifetime of the node [5]. The sensor processors are compact and reliable which can combine sensing, computation, storage, communication and power supplies into small form factors [6]. The sensor operation is dependent on power consumption as the sensors are inevitably used in remote area which is difficult to reach. The limitations of the sensors like reduced lifetime and difficulty in replacement has lead to the development in this field. The future emphasis is to increase the lifespan of the sensor with minimal usage of resources in efficient manner for all applications. Each sensor node operates by collecting the information from the surrounding and transfers them to the base station through wireless transmission. Since power required for the sensor node is more, battery is not sufficient due to its limited capacity. Wind and solar energy sources are not reliable to use although these sources are sufficient for WSN. Hence the design of WSN should use the low power architecture [7]. The basic design architecture of the sensor node consist of storage unit, power unit, transceiver, processing unit and sensing unit as shown in the Figure-1. The power generator is connected the power unit to provide power for the sensor node to operate.

www.arpnjournals.com

Figure-1. Architecture of sensor node.

The energy usage in sensor nodes can be reduced by reducing the duty cycle, dynamically changing the frequency, tuning the radio transceiver selectively. Xilinx and Alter are the two field programmable gate array (FPGA) major in the semiconductor marketplace as they offer up to 28 nm CMOS technology. This development in semiconductor field leads to produce energy efficient computing platforms. In some situation selective operation is enabled by selectively turning on the specific functional modules. Recent FPGAs includes energy efficient arithmetic components such as adders and multipliers operating at high speed with low power consumption.

#### 2. RELATED WORK

The following section consists of several architecture designs for WSN to undergo the survey to obtain the better solution for low power operation of WSN.

Arguments we use to prove Theorem 1 are quite similar to those applied to the embedded Markov chain model of [8]. In that paper, Federgruen and So consider an analogous problem in continuous time with compound Poisson arrivals. By formulating the problem as a semi-Markov decision process embedded at certain decision epochs, they show that either a no vacation policy or a threshold policy is optimal under a weaker set of assumptions. Specifically, they allow general nondecreasing holding costs, multiple arrivals, fixed costs for switching between service and vacation modes, and general i.i.d. service and vacation times. We have not vet explored relaxing our assumptions in a similar manner. By imposing the extra assumptions, however, we have arrived at the more specific conclusion that if the optimal policy is an N-threshold policy, it is indeed a 1-policy. Additionally, we have identified condition (4), distinguishing the parameter sets on which the 0-policy is optimal from those on which the 1-policy is optimal.

A sleep scheduling algorithm based on Qlearning with linear function approximation is proposed in [9]. The algorithm is formulated as a partially-observable Markov decision process with continuous state-action spaces. A best policy to minimize the long-run is devised through incremental updates. The algorithm shows large oscillations when involving high-dimensional state spaces. It involves conflicts of making more number of sensors sleep and more intruder detection at the same time. Also the sensors did not collaborate in the absence of a central controller. A collaborative location-based sleep scheduling scheme for dynamically allocating the sleep/wake state of sensor based on the location of mobile user is presented in [10]. The algorithm sends a flag to the base station based on the current location of mobile user. The sensor nodes go to sleep/wake state according to the flag it receives in each epoch. A sensor node is sleeping scheduled based on the EC-KCKN scheme. Before a node goes into sleep state, the epoch ensures that the node has at least kconnected neighbours.

#### A. SNOC architecture

Robert X. GAO et al developed a new architecture for sensory node controller (SNOC). This node uses dynamic voltage scaling (DVS) mechanism. DVS is used to minimize the energy required for running a given task by dynamically adjusting the supply voltage and the clock speed of the processor according to the time constraints prescribed by each task. Significant energy benefits have been reported by scheduling the computational load and utilizing the CPU idle time. Using DVS the power supply required becomes one fourth of the fixed power supply and the scheduled data acquisition results in the low energy consumption. This mechanism requires special software concept to handle the DVS mechanism in the power unit shown in figure 2. In designing the SNOC software, modularity and flexibility are the main attributes considered for the easy customization and reconfiguration of each SNOC for different applications with minimal overhead. The systemlevel software architecture of an SNOC is divided into three distinct partitions. The event-based energy control partition activates and controls the DVS algorithm for the SNOC operation. The control response to machine defects reported by the monitoring sensors are initiated at the knowledge-based data processing partition and depends on the relationship between physical signals and machine conditions, which are obtained from experimental studies. The data processing results and corresponding features extracted from the sensor data, the operation mode of a sensory node can be modified in situ. For example, when no defect features are identified, SNOC electronics will be forced into the sleep mode by working state control module. Consequently, the energy control module will reduce the supply voltage to the system, thus preserving battery capacity and the programming overhead is increased. This architecture reduces 43% of the energy by comparing with the traditional techniques [5].

## B. Reconfigurable hardware design

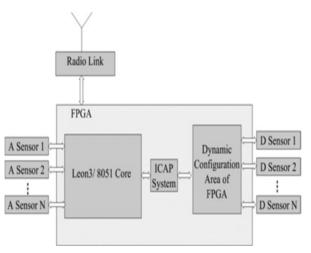

Y. Li Z. Jiao F. Liu S. Xie designed a novel partial dynamic reconfiguration-based WSN node for less

#### www.arpnjournals.com

power consumption. Internal configuration access port (ICAP) is the mechanism to configure the fabric of Xilinx FPGAs. Through ICAP, the internal registers can be accessed and configuration memory can be read and wrote. The ICAP wrapper is the module containing hardware controllers, which function as interaction between the software and ICAP. The ICAP wrapper and ICAP are contained in a module named ICAP Hardware system which is integrated with the rest WSN node. Inside ICAP wrapper, ICAP decoder is the main controller. It distinguishes the data as instructions and data, which are used as partial design reconfiguration (PDR) and send the signal to the corresponding modules in ICAP wrapper. The address controller and ICAP controller are used to control the flow of data within ICAP wrapper as the data can be both sent to the ICAP primitive or read back from ICAP. The data to ICAP primitive is the configuration file for FPGA configuration. The read back data represents the particular design of application for a region of the FPGA, which are pre-stored in configuration memory or data from the internal registers of ICAP. The dual port blocks ram (BRAM) works as buffer memory. Data to be written into ICAP or read back from ICAP are temporally stored into BRAM before it is used. For communicating, ETRX2 module from Telegesis is utilized as it is based on ZigBee and a low-power implementation. Through universal asynchronous receiver transmitter (UART) port, the module is managed by processor. Approximately 31 to 829 mW power can be saved for each implementation. The reconfigurable hardware design is given in Figure-2 in which the ICAP mechanism is implemented in the ICAP system processor module.

Figure-2. Reconfigurable hardware design.

The major part of the processing work is carried by FPGA, which can be configured through JTAG (joint test action group) port. In the second solution, the power consumption significantly reduces. The 8051 core consumes less power than Leon core. The total energy saved is nearly 60% [11].

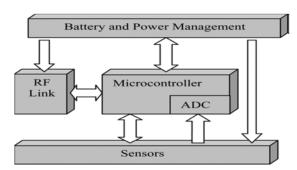

### C. Modular architecture

Rafael et al developed the architecture to reduce the power consumption by designing a miniaturized 3D architecture using cubic structure. The cubic structure fullfills the entire power requirement by the in-built battery by partitioning the node into six functional sub modules such as Sensing, Signal Conditioning, Processing, RF Link, Power and Spare. The first five are the basic building blocks of a standard node. The Spare sub module could be used for extra sensors, antenna mounting, extra memory, programming test connectors or other required extra functions. Each sub module is allocated to a separate circuit board. In the cubic structure, each board is of same size and has same pattern of I/O pads on one, two, or all four sides. This allows the use of a common "bus" layout between each board with a common allocation of power, ground and I/O positions on the "bus." The "bus" is implemented by a short length of single-sided flexible PCB interconnecting each board with its neighbour(s) in an overall cruciform rigid-flex assembly.

Figure-3. Modular architecture.

The battery receptacle is a simple plastic frame. The six circuit boards, interconnected by flex PCB, are folded around the battery receptacle to completely enclose it. Contact to the battery is made by simple spring contacts on the back of the "top" and "bottom" circuit boards. The circuit boards can be clipped, screwed, or (in the case of rechargeable batteries) permanently fixed in place [12].

#### D. SRAM- FPGA-based design

Muhammad Imran et al introduced energy-efficient SRAM FPGA-based wireless vision sensor node (VSN). VSN is designed using static RAM (SRAM) based FPGA when compared to FLASH based FPGA. For conserving energy, the VSN can be switched to a low-power state, referred to as the sleep state, when the required vision tasks have been performed. In sleep state, only the real-time counter is ON in order to keep track of the timing, whereas all other components, i.e., FLASH, FPGA, SRAM, and transceiver are OFF. The minimum sleep duration should be 235 ms in order to effectively utilize the SRAM-based FPGA for duty-cycled VSN applications. The average power consumed is 670 mW. The life time of the microcontroller is ~3.2 years [13].

#### www.arpnjournals.com

#### E. Near-threshold design

Jos Hulzink et al proposed design low power wireless sensor node for biomedical applications. This follows the data driven operations and single instruction multiple data (SIMD) mechanism. The low power consumption is achieved by power optimization at different abstraction layers including application optimization and mapping, system partitioning for effective duty cycling, multi-layer extensive clock gating and circuit level optimization for operating at near threshold and low power on-chip clock generation. There are 15 power domains. The data and program memories are divided into 13 different memory banks which can be individually put in retention mode or switched on or off. The processor is in a separate power domain without retention mode and can be only powered on or off. The rest of the system, including the peripherals, is in one power domain (the periphery domain) which is always on. To control the different domains, the power manager is equipped with two sets of configuration registers. One contains the configuration when the processor is running (awake), the other is used when the processor is switched off and the chip is in data collection mode (asleep). The power manager switches automatically to the asleep state when the processor finishes its running task and back to the awake state when the interrupt controller indicates there is an interrupt pending for the processor. The dynamic power consumed by these sensor nodes vary for different operating modes. High performance consumes more energy than the low performance and the data collection applications. A 13 pJ/cycle of power is achieved for single lead ECG [10].

### F. Variable dual VDD architecture

Jianfeng Zhu et al proposed low power reconfigurable processor utilizing variable dual VDD. The power is reduced by applying variable dual-VDD method. The granularity of dual VDD is selected to be the interconnect, because this module is more power efficient than the ALU. Its POWER/DELAY is ten times larger than that of the ALU. The preferred design is to configure dual VDD for the interconnect rather than the ALU. As shown in figure 5.a two selecting transistors and 2-bit configurations are required to choose power supply from VDDH (the higher VDD) and VDDL and power gating for each interconnect instance. The additional cost of the variable dual-VDD method is an adjustable dc-dc converter. The buck converter and control circuits are adopted to generate the variable VDDL. Its input N is provided by a compiler. The output VDDL can be adjusted through software control. The power consumed is 1.2  $\mu$ W when 0.7 volt is applied [11].

METHODOLOG PROS CONS Required power Increases the Dynamic volta se is one fourth of programming scaling(DVS) the fixed power overhead. supply. Sleep -event wake Security using Applicable un-resemble only. for coder algorithm specific applications Reconfiguring Disconnection complexity while handware programming. Built-in battery in No externa 1 Needs battery systematic wireless sensor require ment approach to node integrate the battery. SRAM FPG A Liffe time Generic extended. architec ture based WSN supporting only duty cycling applications. Partitioning Data driven Very less power consumption of the circuit. me chanism CMOS Variable dua1-Requires transistors are reconfigurabl VDD method e processor

**Table-1.** Shows various comparisons.

#### 3. CONCLUSIONS

In recent year wireless sensor network is the most interesting field for the researcher to contribute the main aim of the routing protocol to improve lifetime of sensor node for the purpose to improve network lifetime. In the

experiment, enhanced QoS and experimental results show that the energy consumption, prolongs the function lifetime, and guarantees high QoS of WSN. Power consumption influences the performance and the lifetime of the sensor nodes in WSN. The above surveyed papers

# ARPN Journal of Engineering and Applied Sciences

© 2006-2017 Asian Research Publishing Network (ARPN). All rights reserved

#### www.arpnjournals.com

present the low power design along with other features such as lifetime enhancement, low area complexity.

#### REFERENCES

- [1] Cardei M., Wu J. 2006. Energy-efficient coverage in wireless ad-hoc networks. Comput. Commun. 29: 413-420.

- [2] Meguerdichian S., Koushanfar F., Potkonjak M., Srivastava M.B. 2001. Coverage problems in wireless ad-hoc sensor networks. Proceedings of INFOCOM. 1380-1387.

- [3] Akyildiz I.F., Weilian S., Sankarasubramaniam Y., Cayirci E. 2002. A survey on sensor networks. IEEE Commun. Mag. 40: 102-114

- [4] A. Federgruen and K. C. So. 1991. Optimality of threshold policies in single server queuing systems with server vacations. Adv. Appl. Prob. 23(2): 388-405.

- [5] NIKOLAOS A. PANTAZIS. A survey on power control issues in Wireless sensor networks. IEEE communications.

- [6] S. G. Shiva Prasad Yadav. Wireless Sensor Networks Architectures, Protocols, Simulators Applications: a Survey. International Journal of Electronics and Computer Science Engineering 1941 ISSN-2277-1956.

- [7] Parool Jain. 2013. A survey on energy optimization in wireless sensor network. International Journal of Engineering Sciences & Emerging Technologies. ISSN: 2231-6604, 5(1): 68-74 ©IJESET.

- [8] Dhanajay A. Sabale, Sushil M. Sakhare. 2014. Wireless Sensor Network for Industrial Process Controlling and Monitoring. International Journal of Electronics Communication Computer Technology (IJECCT). 4(4).

- [9] Robert X. Gao. 2006. Architectural Design of a Sensory Node Controller for Optimized Energy Utilization in Sensor Networks, IEEE transactions on instrumentation and measurement. 55(2).

- [10] Shilong Lu, Xi Huang, Li Cui. 2009. Design and Implementation of an ASIC-based Sensor Device for WSN Applications. IEEE Transactions on Consumer Electronics. 55(4).

- [11] Y. Li Z. Jia F. Liu S. Xie. 2012. Hardware reconfigurable wireless sensor network node with power and area efficiency. IET Wirel. Sens. Syst. 2(3): 247-252.

- [12] Rafael Vicente Martinez-Catalá et al. 2009. A Modular Wireless Sensor Platform with Fully Integrated Battery. IEEE transactions on components and packaging technologies. 32(3).

- [13] A.S.Syed Navaz, J.Antony Daniel Rex, S.Jensy Mary. 2015. Cluster Based Secure Data Transmission in WSN. International Journal of Scientific & Engineering Research. 6(7): 1776-1781.

- [14] A.S. Syed Navaz, P. Jayalakshmi, N. Asha. 2015. Optimization of Real-Time Video Over 3G Wireless Networks" September. International Journal of Applied Engineering Research. 10(18): 39724-39730.

- [15] A.S.Syed Fiaz, N.Asha, D.Sumathi and A.S.Syed Navaz. 2016. Data Visualization: Enhancing Big Data More Adaptable and Valuable. International Journal of Applied Engineering Research. 11(4): 2801-2804.

- [16] A.S.Syed Navaz & Dr.G.M.Kadhar Nawaz. 2016. Flow Based Layer Selection Algorithm for Data Collection in Tree Structure Wireless Sensor Networks. International Journal of Applied Engineering Research. 11(5): 3359-3363.

- [17] A.S.Syed Navaz and Dr. G.M. Kadhar Nawaz. 2016. Layer Orient Time Domain Density Estimation Technique Based Channel Assignment in Tree Structure Wireless Sensor Networks for Fast Data Collection. International Journal of Engineering and Technology. 8(3): 1506-1512.