### ARPN Journal of Engineering and Applied Sciences

© 2006-2017 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

### MULTILEVEL INVERTER TOPOLOGIES FOR PHOTOVOLTAIC POWER SYSTEM: A REVIEW

Usman Bashir Tayab<sup>1</sup> and Muhammad Adnan Bashir<sup>2</sup> <sup>1</sup>University Malaysia Perlis, Perlis, Malaysia <sup>2</sup>University of Agriculture, Faisalabad, Pakistan E-Mail: usman.tayab@yahoo.com

#### ABSTRACT

This paper presents a comprehensive review on three basic types of multilevel inverters i.e., diode-clamped, flying-capacitor, and cascaded H-bridge multilevel inverter and their variation for photovoltaic power system. The electrical power generated form photovoltaic power system is in DC form. Hence, it is necessary to be controlled and converted to useful form. Inverter is a power electronic device which is used to convert the DC power into AC form at desired output voltage and frequency. Multilevel inverters nowadays become interesting area in field of electric power system because it has the capability to produce staircase AC output voltage waveform without using a bulky passive filter. The state of art of multilevel inverter technology for photovoltaic power system has been presented in this paper, which will be very helpful to the researchers to trace the drawbacks in this field of research and thereby will provide information to resolve the existing issues in the near future.

**Keywords:** photovoltaic power system, multilevel inverter, flying-capacitor, diode-clamped, cascaded H-bridge.

#### 1. INTRODUCTION

The demand of clean energy is increasing toward a large distribution of energy generated by renewable energy sources such as solar, wind, hydro, and so on [1]. The sun is the most important source of renewable energy available all over the world. Photovoltaic (PV) power systems convert sunlight to electricity via PV panels. DC power generated by solar panels need to be controlled and converted to usable forms [2-4]. Different types of power inverters have been proposed by researchers. Among them, pulse-width modulated (PWM) multilevel inverters are gaining more and more popularity due to its wide spread reliable applications [5]. Their staircase output voltage consists of low total harmonic distortion (THD) and hence does not require bulky expensive and dissipative passive filters [6-8].

The multilevel inverter can be classified into three basic types such as diode-clamped, flying-capacitor and cascaded H-bridge multilevel inverter [9]. The operation, advantages, and disadvantages of diodeclamped, flying-capacitor and cascaded H-bridge multilevel inverter are discussed in following sections.

The remainder of this paper is organized as follows. In Section 2, the detail description and variation of diode-clamped multilevel inverter is presented. In Section 3, the flying-capacitor multilevel inverter and its modification is discussed. In Section 4, the comprehensive details and modifications of cascaded H-bridge multilevel inverter are provided. The classical diode-clamped, flyingcapacitor, and cascaded H-bridge multilevel inverters are compared in Section 5. Finally, the conclusion is provided in Section 6.

### 2. DIODE-CLAMPED MULTILEVEL INVERTER AND MODIFICATIONS

This section consists of two subsections as follows: a brief description of diode-clamped multilevel inverter and modified diode-clamped multilevel inverter.

### 2.1. Diode-clamped multilevel inverter

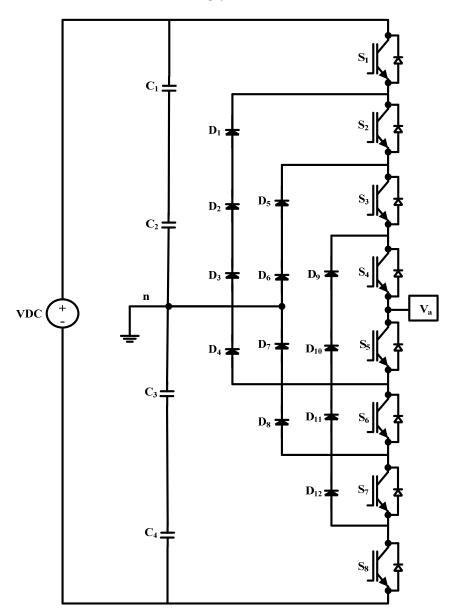

In 1981, the diode-clamped multilevel inverter was introduced by Nabae. First proposed diode-clamped inverter essentially consists of three levels [10]. In the 1990s, researchers published many articles on the experimental results of four, five, and six-level diodeclamped converter for several uses such as, variable speed motor drive, PV power system and high voltage system interconnections [11-12]. Fig. 1 shows the circuit diagram of a 5-level diode clamped multilevel inverter. It consists of eight power MOSFETs, twelve clamping-diodes, one DC voltage source and four capacitors.

Figure-1. 5-level diode-clamped multilevel inverter.

The DC bus consists of four capacitors C1, C2, C3 and C4 as can be seen in Figure-1. For DC bus, each capacitor has VDC/4 voltage and the stress on each power MOSFET will be limited to the voltage level of one

capacitor through clamping diode. The operation of 5-level diode-clamped multilevel inverter depends on switching states of inverter. Table-1 shows the switching states of 5-level diode-clamped inverter [10, 13].

**Table-1.** Switching states of 5-level diode-clamped multilevel inverter.

| $V_{an}$ | S <sub>1</sub> | $S_2$ | S <sub>3</sub> | S <sub>4</sub> | S <sub>5</sub> | S <sub>6</sub> | <b>S</b> 7 | S <sub>8</sub> |

|----------|----------------|-------|----------------|----------------|----------------|----------------|------------|----------------|

| VDC/2    | 1              | 1     | 1              | 1              | 0              | 0              | 0          | 0              |

| VDC/4    | 0              | 1     | 1              | 1              | 1              | 0              | 0          | 0              |

| 0        | 0              | 0     | 1              | 1              | 1              | 1              | 0          | 0              |

| -VDC/4   | 0              | 0     | 0              | 1              | 1              | 1              | 1          | 0              |

| -VDC/2   | 0              | 0     | 0              | 0              | 1              | 1              | 1          | 1              |

(Zero indicate the switch is off and 1 indicate the switch is on)

### ARPN Journal of Engineering and Applied Sciences

© 2006-2017 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

From Table-1, there are five switching combinations for producing the five voltage levels across 'a' and neutral point ('n').

- When  $S_1$ ,  $S_2$ ,  $S_3$  and  $S_4$  are turned on the voltage level "Van" is VDC/2.

- When  $S_2$ ,  $S_3$ ,  $S_4$  and  $S_5$  are turned on the voltage level "Van" is VDC/4

- When S<sub>3</sub>, S<sub>4</sub>, S<sub>5</sub> and S<sub>6</sub> are turned on the voltage level "V<sub>an</sub>" is 0.

- When S<sub>4</sub>, S<sub>5</sub>, S<sub>6</sub> and S<sub>7</sub> are turned on the voltage level "Van" is -VDC/4.

- e) When  $S_5$ ,  $S_6$ ,  $S_7$  and  $S_8$  are turned on the voltage level "Van" is -VDC/2.

The number of power MOSFETs or active switches, S of diode-clamped multilevel inverter is given by the following equation [14]:

Number of power MOSFET (S) = 2\*(m-1). **(1)**

The number of capacitors, C of diode clamped multilevel inverter is given by Eq. (2):

Number of Capacitors (C) =

$$m-1$$

. (2)

The number of clamping diodes, CD of diode clamped multilevel inverter is as follows:

Number of Clamping Diodes (CD) = (m-1)\*(m-2).

Hence, m is number of inverter levels. The advantages and disadvantages of diode-clamped multilevel inverter are given in Table 2 [15-17].

**Table-2.** Advantages and disadvantages of diode-clamped multilevel inverter.

|   | Advantages                                                       | Disadvantages                                                          |

|---|------------------------------------------------------------------|------------------------------------------------------------------------|

| - | <ul> <li>Efficiency is high for fundamental frequency</li> </ul> | <ul> <li>Real power flow is difficult for a single inverter</li> </ul> |

|   | switching.                                                       | because the intermediate DC levels will tend to                        |

| • | <ul> <li>The capacitors can be pre-charged as a</li> </ul>       | overcharge or discharge without precise                                |

|   | group.                                                           | monitoring and control.                                                |

| • | <ul> <li>All of the phases share a common DC bus,</li> </ul>     | <ul> <li>The excessive clamping diode requires if the</li> </ul>       |

|   | which minimizes the capacitance                                  | number of level increased therefore the use of                         |

|   | requirements of the converter.                                   | this inverter is limited to 3-levels.                                  |

### 2.2. Modified diode-clamped multilevel inverter

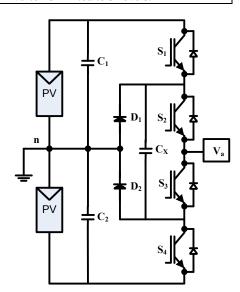

Hybrid-diode-clamped three-level transformerless inverter is another inverter topology for photovoltaic system [18]. It has several benefits such that the PV system has fewer harmonics and the filtering equipment will be reduced at the same time. Moreover, it reduced the losses, costs of the PV system and resolved the leakage current problem. With N inverter modules, the main disadvantage of clamped capacitor topology is imbalance of capacitor voltage in the DC side. In this topology, the capacitor C<sub>X</sub> is used to solve this problem as can be seen from Figure-2.

**Figure-2.** The hybrid clamped three-level inverter.

### 3. FLYING-CAPACITOR MULTILEVEL INVERTER AND MODIFICATIONS

In this section, the operation, advantages, disadvantages and modifications of flying-capacitor multilevel inverter are discussed.

### 3.1. Flying-capacitor multilevel inverter

In 1992, the flying-capacitor multilevel inverter was proposed by Meynard and Foch. The flying-capacitor

### ARPN Journal of Engineering and Applied Sciences

© 2006-2017 Asian Research Publishing Network (ARPN). All rights reserved

### www.arpnjournals.com

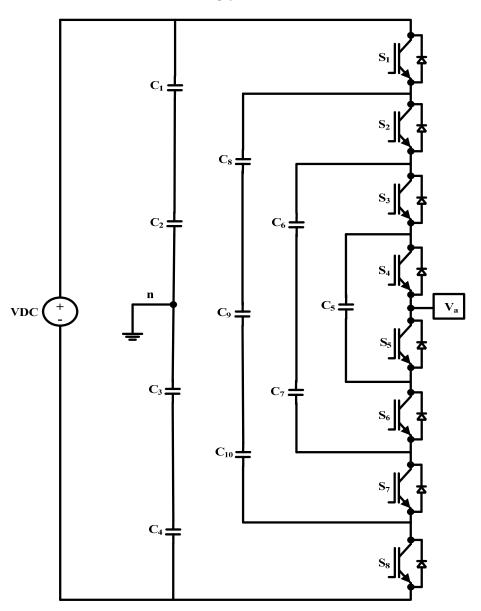

gave large attention for high power application such as PV power system, large motor drives and static power conditioners [19]. Figure-3 shows the circuit topology of 5-level single phase flying-capacitor multilevel inverter. The five-level flying-capacitor has eight MOSFETs, four DC-link capacitors, six balancing capacitors and one DC voltage source.

The operation of five-level flying-capacitor multilevel inverter depends on switching states of inverter. There are many ways to produce the same level of voltage by changing the switching states. It causes redundancy in the switching states of the topology. The sum of a certain output voltage is generated by the DC bus voltage ±VDC/2 and one or more of the clamping capacitor voltages are added together. Since every capacitor is rated for the voltage VDC/4, DC-capacitor and clamping capacitor are identical for the output voltage. For this example, VDC/4 is generated by the DC-bus positive top value VDC/2 and the reverse voltage of clamping capacitor C1. The switching states of 5-level flyingcapacitor inverter are presented in Table-3.

**Table-3.** Switching states of 5-level flying-capacitor multilevel inverter.

| Van    | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | S <sub>5</sub> | <b>S</b> 6 | <b>S</b> 7 | S <sub>8</sub> |

|--------|----------------|----------------|----------------|----------------|----------------|------------|------------|----------------|

| VDC/2  | 1              | 1              | 1              | 1              | 0              | 0          | 0          | 0              |

| VDC/4  | 1              | 1              | 1              | 0              | 1              | 0          | 0          | 0              |

| 0      | 1              | 1              | 0              | 0              | 1              | 1          | 0          | 0              |

| -VDC/4 | 1              | 0              | 0              | 0              | 1              | 1          | 1          | 0              |

| -VDC/2 | 0              | 0              | 0              | 0              | 1              | 1          | 1          | 1              |

(Zero indicate the switch is off and 1 indicate the switch is on)

From Table 3, there are five switching combinations for producing the 5-level voltages across 'a' and 'n'.

- When  $S_1$ ,  $S_2$ ,  $S_3$  and  $S_4$  are turned on the voltage level "Van" is VDC/2.

- When  $S_1$ ,  $S_2$ ,  $S_4$  and  $S_5$  are turned on the voltage level "Van" is VDC/4.

- When S<sub>1</sub>, S<sub>2</sub>, S<sub>5</sub> and S<sub>6</sub> are turned on the voltage level "V<sub>an</sub>" is 0.

- d) When  $S_1$ ,  $S_5$ ,  $S_6$  and  $S_7$  are turned on the voltage level "Van" is -VDC/4.

- When S<sub>5</sub>, S<sub>6</sub>, S<sub>7</sub> and S<sub>8</sub> are turned on the voltage level "Van" is -VDC/2.

The number of MOSFETs or active switches, S of diode clamped multilevel inverter is given by:

Number of MOSFET (S) =

$$2*(m-1)$$

. (4)

The number of DC-link capacitors, C of diode clamped multilevel inverter is given by:

Number of DC-link Capacitors (C) =

$$m-1$$

. (5)

The number of balancing capacitors, BC of flying capacitor multilevel inverter is given by:

Number of Balancing Capacitors (BC) =

$$\frac{(m-1)*(m-2)}{2}$$

.(6)

Hence, m is number of levels. The advantages and disadvantages of flying-capacitor multilevel inverter are given in Table 4 [20-22].

Figure-3. 5-level flying-capacitor multilevel inverter.

Table-4. Advantages and disadvantages of flying-capacitor multilevel inverter.

#### Advantages Disadvantages Real and reactive power Control is complicated to track the voltage flow can be controlled compared to diode-clamped levels for all of the capacitors. multilevel inverter. Pre-charging of all the capacitors to the same For m number of levels, the harmonics voltage level and startup are complex. content is low compared to diode-clamped Efficiency and switching utilization is poor for multilevel inverter. real power transmission. The capability of storage power is high due to Packaging is more difficult for a high number large number of capacitors. of levels due to the requirement of large The large number of capacitors enables the number of components as compared to inverter to ride through short duration outages cascaded H-bridge inverter. and deep voltage sags. The flying-capacitor inverter is often For balancing, the voltage levels of the expensive and bulky compared to the cascaded capacitors several phase redundancies are H-bridge inverter. available.

#### 3.2. Modified flying-capacitor multilevel inverter

To cope the drawbacks of classical flying-capacitor multilevel inverter, the researchers proposed several modified flying-capacitor multilevel inverters based on bridge modular switched-capacitor [23-26]. These topologies require lower number of components as compared to classical flying-capacitor topology. In addition, these topologies have features of voltage balancing property, purge the more dc source, boost-up the output voltage levels, and provide better the output frequency range.

## 4. CASCADED H-BRIDGE MULTILEVEL INVERTER AND MODIFICATIONS

In this section, the operation, advantages, disadvantages and several modifications of cascaded H-bridge multilevel inverters (i.e., Quasi-Z source, switched-capacitor, and switched-battery boost multilevel inverter) are discussed.

### 4.1.Cascaded H-bridge multilevel inverter

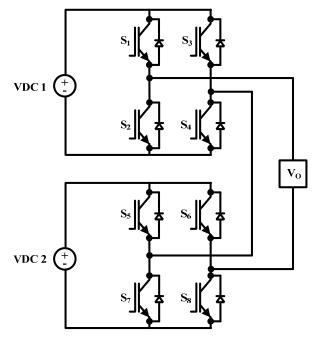

A cascaded H-bridge multilevel inverter is different from diode clamped multilevel inverter and flying capacitor multilevel inverter in structure. The number of output voltage levels can be easily adjusted by adding or removing the H-bridge. H-bridge was introduced in 1975 [7]. It was the first multilevel inverter. In 1996, the cascaded H-bridge multilevel inverter was proposed by Jih-Sheng [27].

Figure-4. 5-level cascaded H-bridge multilevel inverter.

Cascaded H-bridge multilevel inverter is among the most popular inverter topology in stand-alone PV systems. Figure-4 shows 5-level cascaded H-bridge multilevel inverter. H-bridge inverters are connected in series with their output voltages are summed up. Hence, it has voltage boosting capability and highly reliable with lowest voltage unbalance problem. With N number of H-bridge inverters, the output staircase AC voltage produced consists of 2N+1 levels [28]. This inverter topology requires separate DC source for each H-bridge inverter as can be seen from Figure-4.The operation of 5-level cascaded H-bridge multilevel inverter is dependent on switching states of inverter. Table-5 shows the switching states of 5-level cascaded H-bridge multilevel inverter.

**Table-5.** Switching states of 5-level cascaded H-bridge multilevel inverter.

| Vo    | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | S <sub>5</sub> | S <sub>6</sub> | S <sub>7</sub> | S <sub>8</sub> |

|-------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 2VDC  | 1              | 0              | 0              | 1              | 1              | 0              | 0              | 1              |

| VDC   | 1              | 0              | 0              | 1              | 0              | 0              | 1              | 1              |

| 0     | 1              | 1              | 0              | 0              | 1              | 1              | 0              | 0              |

| -VDC  | 0              | 1              | 1              | 0              | 1              | 1              | 0              | 0              |

| -2VDC | 0              | 1              | 1              | 0              | 0              | 1              | 1              | 0              |

(Zero indicate the switch is off and 1 indicate the switch is on)

From Table-5, there are five switching combinations to produce five voltage levels are discussed as follows:

- a) When  $S_1$ ,  $S_4$ ,  $S_5$  and  $S_8$  are turned on the voltage level " $V_0$ " is 2VDC.

- b) When  $S_1$ ,  $S_4$ ,  $S_7$  and  $S_8$  are turned on the voltage level " $V_0$ " is VDC.

- c) When S<sub>1</sub>, S<sub>2</sub>, S<sub>5</sub> and S<sub>6</sub> are turned on the voltage level "V<sub>0</sub>" is 0 or when S<sub>3</sub>, S<sub>4</sub>, S<sub>7</sub> and S<sub>8</sub> are turned on the voltage level "V<sub>0</sub>" is 0.

- d) When  $S_2$ ,  $S_3$ ,  $S_5$  and  $S_6$  are turn on the voltage level " $V_0$ " is -VDC.

### ARPN Journal of Engineering and Applied Sciences ©2006-2017 Asian Research Publishing Network (ARPN). All rights reserved.

### www.arpnjournals.com

e) When  $S_2$ ,  $S_3$ ,  $S_6$  and  $S_7$  are turn on the voltage level " $V_0$ " is -2VDC.

The number of levels, m of cascaded H-bridge multilevel inverter is calculated by following equation:

Number of level (m) =

$$2N+1$$

.

Hence, m is the number of inverters and N is the number of H-bridge inverter. The total number of power MOSFETs can be calculated through Eq. (8). The main advantages and disadvantages of cascaded H-bridge multilevel are discussed in Table 6 [29-31].

Number of MOSFET =

$$2*(m-1)$$

. (8)

**Table-6.** Advantages and disadvantages of cascaded H-bridge multilevel inverter.

(7)

|   | Advantages                                                                                                                                                                                                                     | Disadvantages                                                                                                                                                   |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Less number of components is required to get equal voltage level as compared to diodeclamped and flying-capacitor multilevel inverters.  Extra capacitor and diode are not necessary.  The series of H-bridges makes packaging | Separate DC source are required for each H-bridge. The synchronization of reference and the carrier waveforms is required to communicate between the H-bridges. |

| • | easier with modularized layout.  Due to structural flexibility of cascaded H-bridge, the manufacturing process is cheap and fast.                                                                                              |                                                                                                                                                                 |

## 4.2. Modified cascaded H-bridge multilevel inverter # 1

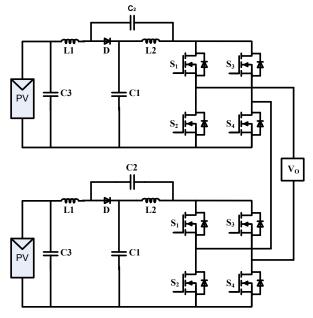

To eliminate the limitations of cascaded H-bridge multilevel inverter, the researchers proposed several modified cascaded H-bridge multilevel inverters based on Quasi-Z source concept [32-38]. Quasi-Z source cascaded H-bridge multilevel inverter (QZS-CHB) is a new topology for PV system. Figure-5 illustrated the structure of PV system based on QZS-CHB multilevel inverter [33]. This system consists of two PV strings, three QZS Hbridge modules, filtering inductance and the distribution grid. The output voltage of the QZS H-bridge multilevel inverter is the sum of all module output voltages. When increasing the number of the QZS H-bridge modules in series, the number of levels of output voltage waveform often increased. The main advantage of this topology is that, it can eliminate the DC-link voltage imbalance problem effectively. The drawbacks of this system are: it consists of large number of components which makes it very complex and costly [32-38].

Figure-5. QZS-cascaded H-bridge multilevel inverter.

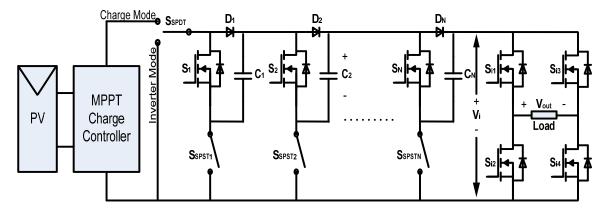

## 4.3. Modified cascaded H-bridge multilevel inverter #2

To eliminate separate DC link, another variation of cascaded H-bridge topology has been proposed which is known as switched-capacitor multilevel inverter. Switched-capacitor (SC) multilevel inverter is useful inverter topology for photovoltaic applications [39-49]. The switched-capacitor (SC) multilevel inverter is composed of series connected switch capacitor cells as shown in Figure-6. A basic SC cells consist of one capacitor, two externally controlled switches and one diode. In this topology, the number of output voltage levels is determined by the number of SC cells. Each cell

adds two voltage levels to output AC voltage waveform. The capacitor and input DC voltage source are connected in parallel during the charged mode while during the discharged mode the capacitors are connected in series via

switching devices. This topology has been proposed for high frequency switching. However, it increased switch losses and required faster switching. Therefore, it has trade off in term of lower efficiency and higher cost.

Figure-6. Series-parallel SC based multilevel inverter.

## 4.4. Modified cascaded H-bridge multilevel inverter # 3

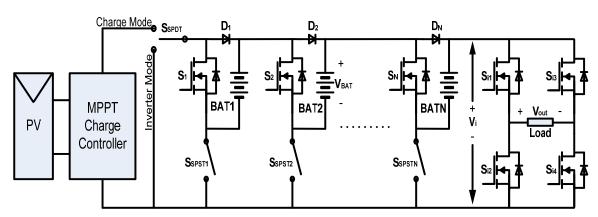

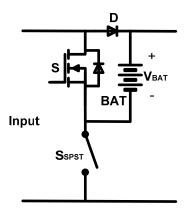

Recently, another modification of cascaded H-bridge multilevel inverter topology is proposed to improve the performance of switched-capacitor multilevel inverter. It is known as switched battery boost multilevel inverter, which consists of a PV module, a MPPT charge controller, a SPDT relay, N number of cascaded switched-battery cells and a full-bridge inverter as shown in Figure-7 [50-52]. Each switched-battery cell consists of a power MOSFET, a diode, a SPST relay and a battery as shown in Figure-8.

This topology can be operated in two different modes such as: charge and inverter mode as controlled by SPDT relay. In order to operate the converter in charge mode, the SPDT relay is switched to MPPT charge controller and all SPST relays are closed while during the charge mode all power MOSFETs are open, all batteries are connected in parallel and store energy generated by PV module. After the batteries are fully charged, the converter can be operated in inverter mode to produce AC voltage and current suitable for most electrical appliances.

Figure-7. Single phase switched-battery boost-multilevel inverter.

Figure-8. Switched-battery cell.

In inverter mode, the MPPT charge controller is connected to the inverter circuit and all SPST relays are off. By turning on the power MOSFETs of switched-battery cells, the batteries are connected in series and total input voltage of H-bridge inverter can be controlled. The number of levels, m of proposed inverter topology is given by

Number of Level =

$$m = 2N+1$$

. (9)

Here, m is the number of inverter level and N is the number of switched-battery cell. The number of power MOSFET required is equal to number of switched-battery cell with additional 4 units for H-bridge inverter. Therefore, total number of power MOSFET is given by

Number of MOSFET =

$$\frac{m-1}{2} + 4$$

. (10)

This inverter topology has high power MOSFET utilization factor as compared to conventional multilevel converter such as cascaded H-bridge multilevel inverter. As an example, a 7-level cascaded H-bridge multilevel inverter requires 12 power MOSFETs while the proposed switched-battery boost-multilevel inverter requires only 7. In addition, this inverter has integrated charge mode operation which is very suitable for PV systems.

# 5. COMPARISON OF BASIC TYPES OF MULTILEVEL INVERTERS

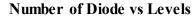

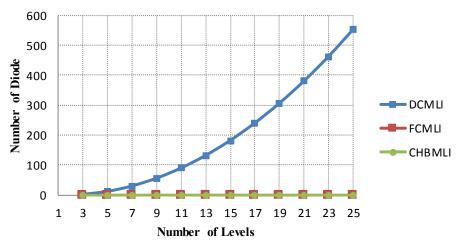

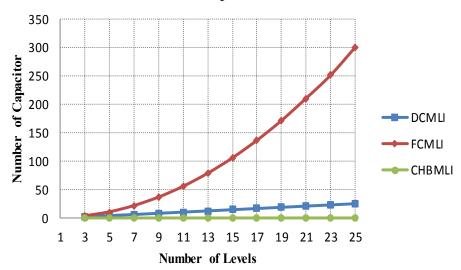

In this section, the comparison between diodeclamped, flying-capacitor, and cascaded H-bridge multilevel inverter is presented. The comparison indicate that the cascaded H-bridge multilevel inverter has gained higher popularity due to several features such as: it does not require an excessively large number of clamping-diode and flying-capacitor. The output voltage levels easily can be controlled by adding or removing the H-bridge. By increasing the number of levels, it produces a multistep staircase voltage waveform which is nearly sinusoidal. The cascaded H-bridge multilevel inverter structure consists of a cascaded connection of H-bridge units and each bridge is fed with separate DC source, therefore it does not require voltage balance circuit. The required number of components for diode-clamped, flyingcapacitor and cascaded H-bridge multilevel inverter are shown in Figure-9(a) to 9(c).

Figure-9(a). Required number of diode for different types of multilevel inverter.

### **Number of Capacitor vs Levels**

Figure-9(b). Required number of capacitor for different types of multilevel inverter.

### **Number of Total Component vs Levels** 700 Number of Total Component 600 500 400 DCM LI 300 **FCMLI** 200 - CHBMLI 100 0 1 3 5 11 13 15 17 19 Number of Levels

Figure-9(c). Required number of total components for different types of multilevel inverter.

Figure-9(a) shows that the clamping diode is required only for diode-clamped multilevel inverter and Figure-9(b) shows that the balancing capacitor is required for diode-clamped and flying-capacitor multilevel inverter. The lower number of components is required for cascaded H-bridge multilevel inverter which can be seen from Figure-9(c). Due to lower number of component cascaded H-bridge multilevel inverter has recently become most popular topology in high AC power supplies and PV system. In addition, the probability of system failure is decreases and control of the switches is not complicated.

### 6. CONCLUSIONS

The paper demonstrates a comprehensive discussion on basic multilevel inverter topologies, and their variations. In addition to that the basic types of

multilevel inverters are compared from different aspects. Classical multilevel inverter structures including the advantages and disadvantages of each technique have been discussed. The main advantage of multilevel inverter is that it provides a solution to the problems of THD, and dv/dt stress on switch. Based on proceeding discussion, it can be concluded that cascaded multilevel inverters require minimum number of components compared with other types of multilevel inverters. So it produces an increased stepped output with less number of semiconductor switches. The control of the overall circuit becomes less complex and smaller due to fewer number of switches.

### ARPN Journal of Engineering and Applied Sciences © 2006-2017 Asian Research Publishing Network (ARPN). All rights reserved.

### www.arpnjournals.com

#### REFERENCES

- S. Daher, J. Schmid, F.L.M. Antunes. 2008.

Multilevel inverter topologies for stand-alone PV systems. IEEE T. Power. Electron. 55: 2703-2712.

- [2] S.B. Kjaer, J.K. Pedersen, S. Member, F. Blaabjerg. 2005. A review of single-phase grid-connected inverters for photovoltaic modules. IEEE T. Ind. Appl. 41: 1292-1306.

- [3] I. Colak, E. Kabalci, R. Bayindir. 2011. Review of multilevel voltage source inverter topologies and control schemes. Elsevier J. Energy Convers. Manage. 52: 1114-1128.

- [4] Y. Zhou, H. Li. 2014. Analysis and suppression of leakage current in cascaded-multilevel-inverter-based PV systems. IEEE T. Power. Electron. 29: 5265-5277.

- [5] J. Lai, S. Member, F.Z. Peng. 1996. Multilevel converters-a new breed of power converters, IEEE T. Ind. Appl. 32: 509-517.

- [6] C. Cecati, F. Ciancetta, P. Siano. 2010. A multilevel inverter for photovoltaic systems with fuzzy logic control. IEEE T. Ind. Electron. 57: 4115-4125.

- [7] R. H. Bannister. 1975. Electric Power Converter, Prentice Hall.

- [8] K.K. Gupta, A. Ranjan, P. Bhatnagar, L.K. Sahu, S. Jain. 2016. Multilevel inverter topologies with reduced device count: a review. IEEE T. Power Electron. 31: 135-151.

- [9] M.H. Rashid. 2003. Power Electronics Circuits Devices and Applications. 3<sup>rd</sup> ed. Pearson/Prentice Hall

- [10] A. Nabae, I. Takahashi, H. Akagi. 1981. A new neutral-point-clamped PWM inverter, IEEE T. Ind. Appl. IA-17: 518-523.

- [11] K.H. Jung, L.H. Dong, S.S. Ki. 2001. A new PWM strategy for common-mode voltage reduction in neutral-point-clamped inverter-fed AC motor drives.IEEE T. Ind. Appl. 37: 1840-1845.

- [12] C. Xia, G. Zhang, Y. Yan, X. Gu, T. Shi, X. He. 2016. Discontinuous space vector PWM strategy of neutral-point-clamped three-level inverters for output current ripple reduction. IEEE T. Power. Electron. 36: 1-10.

- [13] R. Mahalakshmi, K.C.S. Thampatty. 2015. Grid connected multilevel inverter for renewable energy applications. Procedia Tech. 21: 636-642.

- [14] Q. Li, P. Wolfs. 2008. A review of the single phase photovoltaic module integrated converter topologies with three different DC link configurations. IEEE T. Power. Electron. 23: 1320-1333.

- [15]E. Ozdemir, S. Ozdemir, L.M. Tolbert. 2009. Fundamental-frequency-modulated six-level diodeclamped multilevel inverter for three-phase standalone photovoltaic system. IEEE T. Ind. Electron. 56(2009) 4407-4415.

- [16] G.P. Adam, S.J. Finney, B.W. Williams. 2012. Quasitwo-level and three-level operation of a diodeclamped multilevel inverter using space vector modulation. IET Power Electron. 5: 542-551.

- [17] J. Rodriguez, S. Bernet, P.K. Steimer, I.E. Lizama. 2010. A survey on neutral-point-clamped inverters. IEEE T. Ind. Electron. 57: 2219-2230.

- [18] S.B. Monge, J. Rocabert, P. Rodríguez, S. Alepuz, J. Bordonau. 2008. Multilevel hybird-clamped converter for photovoltaic generators with independent voltage control of each solar array. IEEE T. Ind. Electron. 55: 2713-2723.

- [19] T.A. Meynard, H. Foch. 1992. Multilevel conversion: high voltage choppers and voltage-source inverters. In Power Electron. Spec. Conf., 1992, 23rd IEEE. 39: 1397-403.

- [20] J. Amini, M. Moallem. 2016. A fault-diagnosis and fault-tolerant control scheme for flying capacitor multilevel inverters, IEEE T. Ind. Electron. Early access.

- [21] J. Amini, A.H. Viki and A. Radan. 2015. An active capacitor voltage control for symmetrical / nonsymmetrical H-bridge flying capacitor multilevel inverter, In 6<sup>th</sup> Power Electron., Drive Syst. & Tech. Conf. pp. 125-130.

- [22] E.I. Silva, B.P. McGrath, D.E. Quevedo, G.C. Goodwin. 2007. Predictive control of a flying capacitor converter, In American. Control Conf. pp. 3763-3768.

- [23] D.H. Park, N.J. Ku, R. Y. Kim. 2015. A novel switching loss minimization method for single-phase

## ARPN Journal of Engineering and Applied Sciences ©2006-2017 Asian Research Publishing Network (ARPN). All rights reserved.

### www.arpnjournals.com

- flying-capacitor multilevel inverter. In IEEE 2<sup>nd</sup> Int. Fut. Energy Electron. Conf. pp. 1-6.

- [24] N. Maheshkumar, V. Maheskumar, M. Divya. 2013. The new topology in flying capacitor multilevel inverter. In Int. Conf. Comput. Comm. Info. pp. 1-6.

- [25] S.S. Priyan, K. Ramani. 2013. Implementation of closed loop system for flying capacitor multilevel inverter with stand-alone photovoltaic input. In Int. Conf. Power, Energy & Control. pp. 281-286.

- [26] M. Trabelsi, L.B. Brahim. 2011. Development of a grid connected photovoltaic power conditioning system based on flying capacitors inverter. In 8<sup>th</sup> Int. Multi-Conf. Syst. Sig. & Dev. pp. 1-6.

- [27] L.J. Sheng and P.F. Zheng. 1996. Multilevel converters-a new breed of power converters. IEEE T. Ind. Electron. 32: 509-517.

- [28] M. Sadikin, T. Senjyu, A. Yona. 2013. High-frequency link DC for power quality improvement of stand-alone PV system in cascaded multilevel inverter. In IEEE 10<sup>th</sup> Int. Conf. Power Electron. & Drive Syst. 597-601.

- [29] E. Babaei, S.H. Hosseini, G.B. Gharehpetian, M.T. Haque and M. Sabahi. 2007. Reduction of DC voltage sources and switches in asymmetrical multilevel converters using a novel topology, Elsevier J. Electric Power Syst. Res. 77: 1073-1085.

- [30] L.A. Tolbert, P.F. Zheng, T. Cunnyngham and J.N. Chiasson. 2002. Charge balance control schemes for cascade multilevel converter in hybrid electric vehicles. IEEE T. Ind. Electron. 49: 1058-1064.

- [31] E. Villanueva, P. Correa, J. Rodriguez, M. Pacas. 2009. Control of a single-phase cascaded H-bridge multilevel inverter for grid-connected photovoltaic systems. IEEE T. Ind. Electron. 56: 4399-4406.

- [32] Y. Liu, B.G. Ferreira, A.T. Almeida, H.A. Rub. 2011. Modeling and SVPWM control of quasi-z-source inverter, In 11<sup>th</sup> Int. Conf. Electric. Power Quality. & Utilization. pp. 1-7.

- [33] S. Dongsen, G. Baoming, F.Z. Peng, A.R. Haitham, B. Daqiang, L. Yushan. 2012. A new grid-connected PV system based on cascaded H-bridge quasi-z source inverter. In IEEE Int. Symp. Ind. Electron. pp. 951-956.

- [34] Y. Liu, H.A. RuB, F.Z. Peng. 2013. A modular multilevel space vector modulation for photovoltaic quasi-z-source cascade multilevel inverter, In 28<sup>th</sup> Ann. IEEE Appl. Power Electron. Conf. & Expo. pp. 714-718.

- [35] M. Mosa, H.A. Rub, J. Rodríguez. 2013. High performance predictive control applied to three-phase grid connected quasi-z-source inverter, In 39<sup>th</sup> Ann. Conf. IEEE Ind. Electron. Soc. pp. 5812-5817.

- [36] Y. Liu, H.A. Rub, F.Z. Peng. 2014. An effective control method for quasi-z-source cascade multilevel inverter-based grid-tie single-phase photovoltaic power system. IEEE T. Ind. Info. 10: 399-407.

- [37] Y. Liu, H.A. Rub, F.Z. Peng. 2014. An effective control method for three-phase quasi-z-source cascaded multilevel inverter based grid-tie photovoltaic power system. IEEE T. Ind. Electron. 61: 6794-6802.

- [38] D. Sun, B. Ge, X. Yan, D. Bi, H. Zhang, Y. Liu, H.A. Rub, L.B. Brahim, F.Z. Peng. 2014. Modeling, impedance design, and efficiency analysis of quasi-z source module in cascaded multilevel photovoltaic power system.IEEE T. Ind. Electron. 61: 6108-6117.

- [39] E. Zamiri, N. Vosoughi, S.H. Hosseini, R. Barzegarkhoo, M. Sabahi. 2016. A new cascaded switched-capacitor multilevel inverter based on improved series-parallel conversion with less number of components. IEEE T. Ind. Electron. 63: 3582-3594.

- [40] C. Marouchos, M. Darwish, M.S. Moghadam, M. Georgiou. 2015. A new switched capacitor inverter for stand-alone photovoltaic applications. In 50<sup>th</sup> Int. Uni. Power Eng. Conf. 1-4.

- [41] C.C. Marouchos, M. Darwish, L. Diomidou. 2013. A new concept for a multilevel switched capacitor sinusoidal grid connected inverter. In 48<sup>th</sup> Int. Uni. Power Eng. pp. 1-6.

- [42] J. Liu, K.W.E. Cheng, Y. Ye. 2014. A cascaded multilevel inverter based on switched-capacitor for high-frequency AC power distribution system.IEEE T. Power Electron. 29: 4219-4230.

- [43] M.F. Kangarlu, E. Babaei. 2013. A generalized cascaded multilevel inverter using series connection of sub-multilevel inverters. IEEE T. Power Electron. 28: 625-636.

### ARPN Journal of Engineering and Applied Sciences © 2006-2017 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

- [44] K.V. Korotkih, N.N. Lopatkin. 2013. Design of a teaching-research laboratory breadboard for studying of the multilevel voltage inverter with switched capacitors. In: 14<sup>th</sup> Int. Conf. Young Spec. Micro/Nanotech. Electron. Dev.305-309.

- [45] J. Ebrahimi, E. Babaei, G.B. Gharehpetian. 2012. A new multilevel converter topology with reduced number of power electronic components. IEEE T. Ind. Electron. 59: 655-667.

- [46] E. Babaei, F. Sedaghati. 2011. Series-parallel switched-capacitor based multilevel inverter, In Int. Conf. Electric. Mach. & Syst. pp. 1-5.

- [47] Y. Hinago, H. Koizumi. 2010. A single-phase multilevel inverter using switched series/parallel DC voltage sources, IEEE T. Ind. Electron. 57: 2643-2650.

- [48] E. Babaei, S. Alilu and S. Laali. 2014. A new general topology for cascaded multilevel inverters with reduced number of components based on developed H-bridge. IEEE T. Ind. Electron. 61: 3932-3939.

- [49] E. Babaei, S.S. Gowgani. 2014. Hybrid multilevel inverter using switched capacitor units. IEEE T. Ind. Electron. 61: 4614-4621.

- [50] K.K. Gupta, S. Jain. 2014. A novel multilevel inverter based on switched DC sources. IEEE T. Ind. Electron. 61: 3269-3278.

- [51] M.A. Yusof, Y.C. Tan, M. Othman, S.S. Lee, M.A. Roslan, S.L. Ong, J.H. Leong. 2015. Comparison of switching angle arrangement techniques in singlephase boost multilevel inverter for low THD operation, Appl. Mater. Mech. 793: 167-171.

- [52] S.S. Lee, B. Chu, N.R.N. Idris, H.H. Goh, Y.E. Heng. 2016. Switched-battery boost-multilevel inverter with GA optimized SHEPWM for standalone application. IEEE T. Ind. Electron. 63: 2133-2142.