# ARPN Journal of Engineering and Applied Sciences

©2006-2017 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

# ENERGY BALANCE CASCADED MULTILEVEL INVERTER FOR PHOTOVOLTAIC APPLICATION

A. Santhi Mary Antony, D. Ramya and D. Godwin Immanuel Department of Electrical and Electronics, Sathyabama University, Chennai, India E-Mail: msanthimary@gmail.com

#### ABSTRACT

Energy balance cascaded multilevel inverter for photovoltaic application. It is used for less no of power switches, losses, installation area, voltage stress and converter cost. It is also used for solar energy that is connected to the micro grid system. It reduces the transformerless operation and improves the power quality. Ability to operate in both symmetrical and asymmetrical mode is analyzed. The results are done with cascaded H bridge (CHB) and flying capacitor (FC) multilevel inverters. The simulation is done with Matlab Simulink.

Keywords: multilevel inverter, cascaded H Bridge, least power point tracking, buck boost converter.

## 1. INTRODUCTION

In the current scenario, due to the environmental issues and limited fossil resources, the demand for renewable energy is increasing. To meet this growing demand, Photovoltaic (PV), Fuel Cell and Wind Turbine (WT) systems have become the important integral part of grid connected renewable energy systems (RES). Harnessing of electrical energy from the PV systems contributes to power generation. This contribution made it wide spread in the current global climatic conditions. Long lasting, high efficiency and pollution free power generation are the advantages of PV systems. The low output voltage PV arrays are connected in series to accomplish high voltage DC, and DC to AC inverter is used to interface with the grid. This approach needs high voltage rated devices for the inverter. To overcome this issue, the step-up transformer is necessary. This system enables to use the low voltage rated devices for inverter and then boosting the voltage by transformer. This may lead to increase in losses and cost of the system. Using transformerless concepts are beneficial in reducing cost, size, weight and complexity of inverter besides enhancing the efficiency. A multilevel converter is the one which uses properly connected power semiconductor devices to several lower DC voltage sources to synthesize a near sinusoidal staircase voltage waveform. The small output voltage step results in high quality output voltage, reduction of voltage stresses on power switching devices, lower switching losses and higher efficiency. The era of multilevel inverters (MLIs) started with diode clamped multilevel inverter, also known as neutral point clamped (NPC), in 1981 [1], then capacitor-clamped multilevel inverter or flying capacitor in 1992 [2] and the cascade Hbridge (CHB) multilevel inverter in 1995. The different topology presented in the literature as multilevel converters [3-4] possesses the number of characteristics, giving their clear advantages over bi-level converters. These advantages promote the MLIs as the suitable choice for grid connected renewable energy systems in both the adoption of MLIs results in reduction of cost and size of filtering requirements in transformer less PV system depicted in Figure-1 [5-7]. Various MLI topologies for renewable energy applications are listed in [8-10]. The complexity and requirement of high number of power switches are the main disadvantages associated with the multilevel configurations. The reduction of semiconductor switches in the MLI topologies has lead to enormous significance in academia and the industry. The reduction in switches further reduces the number of components including gate drives. Eventually the reduction in switch count improves the efficiency and minimizes the control complexity.

# 2. CIRCUIT DIAGRAM AND SYSTEM MODULE DESCRIPTION

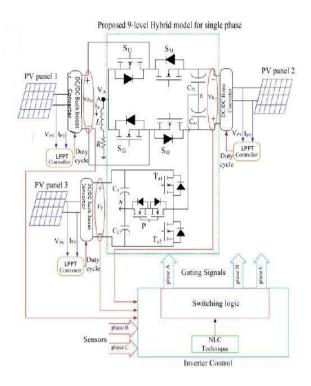

To discuss the impact of removing a PV panel for the purpose of maintenance or failure due to faults [4-9] on the behavior of overall inverter, the PV RES connected to proposed 9-level HCM MLI for single phase. In each phase of proposed inverter connected RES three PV panels viz., 1, 2 and 3 are employed. The sensors are provided at the buck boost converter end to detect the voltage and given to inverter control block. The switching logic is updated in the inverter control block to maintain the three phase balanced output voltages under faulty conditions. Three possible failures or removal are considered in this section and simulation results are presented.

©2006-2017 Asian Research Publishing Network (ARPN). All rights reserved.

### www.arpnjournals.com

Figure-1.

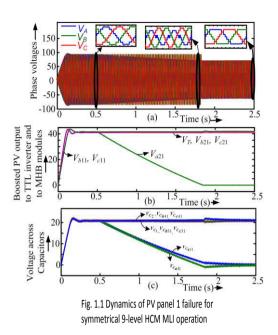

When PV panel 1 is failed to pump the voltage  $V_{a11}$  due to the fault the phase A voltage gets distorted and level gets reduced resulting in unbalance in the three phase system. These dynamics are analyzed with the help of simulation studies presented in the Figure-2 (a)-(c). As shown in Figure-2 (a) the system enters into steady state after t=0.35 sec and producing balanced three phase voltages. When a fault is introduced by setting the PV panel 1 irradiance to zero at t=0.5 sec, the corresponding panel 1 voltage  $V_{a11}$  gradually reduced to zero at t=1.2 sec as seen from the Figure-2 (b). The phase \_A' voltage gets distorted resulting in a reduced fundamental voltage of 35.51V unlike the fundamental at normal operation of 83.87V and increased %THD from 8.40% to 41.74%.

To balance the system, the switching logic in Table-3 is updated according to the Table XI at t=1.4 sec. The system is well balanced and producing 5-levels in all three phases with the improvement of %THD to 17.5% and fundamental is increased to 46.93V. During these changes, the balancing of capacitors is unfazed as shown.

Figure-2(a).

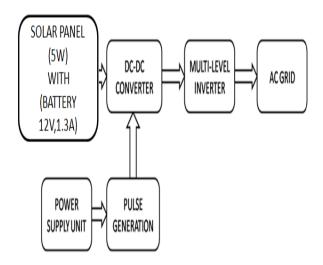

## 3. BLOCK DIAGRAM

Figure-2(b).

## 4. MODES OF OPERATION

To discuss the impact of removing a PV panel for the purpose of maintenance or failure due to faults [4-9] on the behavior of overall inverter, the PV RES connected to proposed 9-level HCM MLI for single phase is shown in Figure-3. In each phase of proposed inverter connected RES three PV panels viz., 1, 2 and 3 are employed. The sensors are provided at the boost converter end to detect the voltage and given to inverter control block. The switching logic is updated in the inverter control block to maintain the three phase balanced output voltages under faulty conditions. Three possible failures or removal are considered in this section and simulation results are presented.

When PV panel 1 is failed to pump the voltage  $V_{a11}$  due to the fault the phase A voltage gets distorted

## www.arpnjournals.com

and level gets reduced resulting in unbalance in the three phase system. These dynamics are analyzed with the help of simulation studies presented in the Figure-3 (a)-(c). As shown in Figure-3 (a) the system enters into steady state after t=0.35 sec and producing balanced three phase voltages. When a fault is introduced by setting the PV panel 1 irradiance to zero at t=0.5 sec, the corresponding panel 1 voltage  $V_{a11}$  gradually reduced to zero at t=1.2 sec as seen from the Figure-3(b). The phase \_A' voltage gets distorted resulting in a reduced fundamental voltage of 35.51V unlike the fundamental at normal operation of 83.87V and increased %THD from 8.40% to 41.74%. To balance the system, the switching logic in Table-1 is updated according to the Table-2 at t=1.4 sec. The system is well balanced and producing 5-levels in all three phases with the improvement of %THD to 17.5% and fundamental is increased to 46.93V. During these changes, the balancing of capacitors is unfazed.

Table-1.

# **BALANCED SYSTEM**

| SYMMETRICAL 9-LEVEL MLI. |           |           |           |           |          |                 |   |         |  |  |  |

|--------------------------|-----------|-----------|-----------|-----------|----------|-----------------|---|---------|--|--|--|

| L.NO.                    | $S_{all}$ | $S_{a21}$ | $S_{a31}$ | $S_{a41}$ | $T_{al}$ | T <sub>a2</sub> | P | $V_{A}$ |  |  |  |

| $l_1$                    | 1         | 0         | 0         | 1         | 1        | 0               | 0 | +2V     |  |  |  |

| 2                        | 1         | 0         | 0         | 1         | 0        | 0               | 1 | +3V/2   |  |  |  |

| 3                        | 1         | 0         | 0         | 1         | 0        | 1               | 0 | +V      |  |  |  |

| 4                        | 0         | 1         | 0         | 1         | 0        | 0               | 1 | +V/2    |  |  |  |

| 5                        | 1         | 0         | 1         | 0         | 1        | 0               | 0 | 0       |  |  |  |

| 6                        | 1         | 0         | 1         | 0         | 0        | 0               | 1 | -V/2    |  |  |  |

| 7                        | 0         | 1         | 1         | 0         | 1        | 0               | 0 | -V      |  |  |  |

| 8                        | 0         | 1         | 1         | 0         | 0        | 0               | 1 | -3V/2   |  |  |  |

| 9                        | 0         | 1         | 1         | 0         | 0        | 1               | 0 | -2V     |  |  |  |

# 5. LPPT (least power point tracking)

It is used for faster than the MPPT in power tra dynamics for the failure of PV panel 2 at t=0.5 sec are shown in Figure-2 (a)-(b). Since the capacitors are connected across the PV panel 2,  $V_{a21}$  takes more time to settle down to zero at t=1.78 sec as depicted in Figure-2(b) and correspondingly the capacitor voltages settle down to zero, while the other capacitor voltages are balanced as shown in Figure-2 (b). The unbalance occurs in system due to Phase \_A'and it is rectified by updating the switching states as per the Table-1. The balance is achieved by synthesizing 7- level in other phases \_B'and \_C'with updating entries of Table-2. The Phase \_A' is recovered from distortion as shown in Figure-2(a) and

improves the fundamental voltage from 58.04V to 71.43V and %THD from 24.71% to 14.14%.

Table-2. Unbalanced system.

| S.NO. | Sall | Sa2l | Sall | Sa41 | Tal | Ta2 | P | $V_A$ |

|-------|------|------|------|------|-----|-----|---|-------|

| 1     | 0    | 1    | 0    | 1    | 1   | 0   | 0 | +V    |

| 2     | 0    | 1    | 0    | 1    | 1   | 0   | 0 | +V    |

| 3     | 0    | 1    | 0    | 1    | 0   | 0   | 1 | +V/2  |

| 4     | 0    | 1    | 0    | 1    | 0   | 0   | 1 | +V/2  |

| 5     | 1    | 0    | 1    | 0    | 1   | 0   | 0 | 0     |

| 6     | 1    | 0    | 1    | 0    | 0   | 0   | 1 | -V/2  |

| 7     | 1    | 0    | 1    | 0    | 0   | 0   | 1 | -V/2  |

| 8     | 1    | 0    | 1    | 0    | 0   | 1   | 0 | -V    |

| 9     | 1    | 0    | 1    | 0    | 0   | 1   | 0 | -V    |

### 5. LPPT (least power point tracking)

It is used for faster than the MPPT in power tracking. The optimal sting current for LPPT changes based on the PV modules operating points which will vary during MPPT. In contrast, each PV modules MPPT is not affected by sting current variation. The LPPT algorithm aims to dynamically track the unique LPPT according to the instantaneous PV voltage and current in the system.

The dynamic response of LPPT should be designed such that one of the algorithms is significantly slower relative to the other algorithm. We can use LPPT in low power appliances for examples kitchen appliances Speakers, LED light etc.

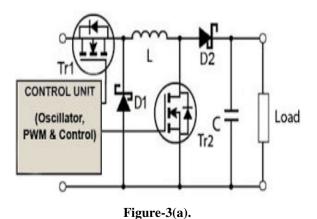

# 6. BUCK-BOOST CONVERTER

The buck-boost converter is a type of DC-to-DC converter that has an output voltage magnitude that is either greater than or less than the input voltage magnitude. It is equivalent to a flyback converter using a single inductor instead of a transformer. A 2-switch buck-

# ARPN Journal of Engineering and Applied Sciences

©2006-2017 Asian Research Publishing Network (ARPN). All rights reserved.

## www.arpnjournals.com

boost converter can be built with two diodes, but upgrading the diodes to FET transistor switches doesn't cost much extra while due to lower voltage drop the efficiency improves. The operation of the buck-boost is best understood in terms of the inductor's "reluctance" to allow rapid change in current. From the initial state in which nothing is charged and the switch is open, the current through the inductor is zero. When the switch is first closed, the blocking diode prevents current from flowing into the right hand side of the circuit, so it must all flow through the inductor. However, since the inductor doesn't like rapid current change, it will initially keep the current low by dropping most of the voltage provided by the source. Over time, the inductor will allow the current to slowly increase by decreasing its voltage drop. Also during this time, the inductor will store energy in the form of a magnetic field.

# 7. SOFTWARE REQUIREMENTS

- MATLAB 7.14

- **MPLAB**

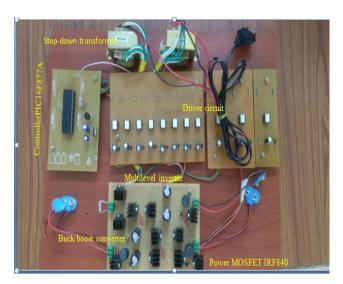

# 8. HARDWARE REQUIREMENTS

Power MOSFET: IRF840

Driver IC : IR2112

Capacitor : 470uF (25V); 1000uF

Controller :PIC16F877A

Regulators :LM7805; LM7812

Diodes : 1N4000; 1N5408

Inductors :100uH; 200uH; 1mH

# 9. EXPERIMENTAL RESULTS

The experimental circuit of the proposed converter is developed. The experimental result of input voltage, input current and output voltage is shown in Figure.

Figure-3(b)

## **CONCLUSIONS**

The experimental results show the ability of a proposed inverter to generate all the levels in both symmetrical and asymmetrical modes while maintaining the natural balancing of all the capacitors voltages in each module. Due to its modular structure, it can be easily interfaced with PV connected micro grid.

## REFERENCES

- [1] R. H. Baker. 1981. Br, U.S. Patent 4 270 163, May. briidge converter circuit.

- [2] T.A. Meynard and H. Foch. 1992. Multi-level conversion: high voltage choppers and voltage-source inverters. In Power Electronics **Specialists** Conference, 1992. PESC '92 Record. 23rd Annual IEEE. 1: 397-403.

- [3] H. Abu-Rub, J. Holtz, J. Rodriguez and G. Baoming. 2010. Medium-Voltage Multilevel Converters-State of the Art, Challenges, and Requirements in Industrial Applications. IEEE Trans. Ind. Electron. 57(8): 2581-2596.

- [4] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franqucelo, B. Wu, J. Rodrigues, M. A.Perez and J. I. Leon 2010. Recent advances and industrial applications of multilevel converters. IEEE Trans. Ind. Electron. 57(8): 2553-2580.

- [5] Alireza Nami and Firuz Zare. 2009. Multilevel Converters in Renewable Energy Systems. | INTECH Open Access Publisher. pp. 271-297, ISBN: 978-953-7619-52-7.

- [6] T. Kerekes, M. Liserre, R. Teodorescu, C. Klumpner and M. Sumner. 2009. Evaluation of Three-Phase

# ARPN Journal of Engineering and Applied Sciences

©2006-2017 Asian Research Publishing Network (ARPN). All rights reserved.

#### www.arpnjournals.com

Transformerless Photovoltaic Inverter Topologies. IEEE Trans. Power Electron. 24(9): 2202-2211.

- [7] M. Coppola, F. D. Napoli, P. Guerriero, D. Iannuzzi, S. Daliento and A. Del Pizzo. 2016. An FPGA-Based Advanced Control Strategy of a GridTied PV CHB Inverter. IEEE Trans. Power Electron. 31(1): 806-816.

- [8] Li Quan and P. Wolfs. 2008. A Review of the Single Phase Photovoltaic Module Integrated Converter **Topologies** with Three Different DC Configurations. IEEE Trans. Power Electron. 239(3): 1320-1333.

- [9] R. Haroun, A. El Aroudi, A. Cid-Pastor, G. Garica, C. Olalla and L. Martinez-Salamero. 2015. Impedance Matching in Photovoltaic Systems Using Cascaded Boost Converters and Sliding-Mode Control. IEEE Trans. Power Electron. 30(6): 3185-3199.

- [10][10] Cheng-Wei Chen, Chien-Yao Liao, Kun-Hung Chen, and Yaow-Ming Chen. 2015. Modeling and Controller Design of a Semiisolated Multiinput Converter for a Hybrid PV/Wind Power Charger System. IEEE Trans. Power Electron. 30(9): 4843-4853.

- [11] D. Gonzalez Montoya, C. A. Ramos-Paja and R. Giral. 2016. Improved Design of Sliding-Mode Controllers Based on the Requirements of MPPT Techniques. IEEE Trans. Power Electron. 31(1): 235-247.

- [12] S. M. Reza Tousi, M. H. Moradi, N. S. Basir, and M. Nemati. 2016. A Function-Based Maximum Power Point Tracking Method for Photovoltaic Systems. IEEE Trans. Power Electron. 31(3): 2120-2128.