## ARPN Journal of Engineering and Applied Sciences

©2006-2018 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

### A 3.4 GHZ FAST-LOCKING PLL USING TRANSMISSION GATE CHARGE-PUMP IN 0.18µM CMOS FOR HDMI APPLICATIONS

Ramanjaneyulu Ningampalli, Satyanarayana Donti and Satya Prasad Kodati Department of Electrical Communication Engineering, RGMCET, Nandyal, Andhra Pradesh, India Email: ramanjaneyulu@rgmcet.edu.in

#### ABSTRACT

A 3.4 GHz Phase Locked Loop (PLL) with a Differential Ring oscillator is simulated in a 0.18µm CMOS process with 1.8V power supply. The reference clock frequency is 212.5 MHz with a mod 16 frequency divider the PLL generates a 3.4 GHz frequency. The proposed PLL can be locked from 2.539 GHz to 5.0793 GHz with a lock range of 2.54 GHz with 48.4% of duty cycle. The peak-peak jitter is 8.786ps with an RMS jitter of 1.18 ps and pull-in time 170ns (fast lock-in time). The PLL consumes 18.8mW power from a 1.8V power supply. PLL Blocks are simulated with 1.8V, 0.18µm CMOS Technology using Cadence-Virtuoso tool.

Keywords: HDMI, Phase frequency detector, charge pump, delay cell, voltage controlled oscillator, PLL.

#### 1. INTRODUCTION

The High-Definition Multimedia Interface (HDMI) is used for transmitting digital television audiovisual signals from DVD players, set-top boxes and other audiovisual sources to television sets, projectors and other video displays [1]. In order to achieve such high accuracy and reliability, HDMI uses Transition minimized Differential Signaling (TMDS) [2] to move information from one place to another. In this scheme, the data is encoded so as to reduce the number of 0-1 transition which in turn reduces the inter-symbol interference [3]. The required specifications as per the HDMI Specification version 1.4 are given in the Table-1.

**Table-1.** HDMI 1.4 specifications.

| Parameter                                            | value          |

|------------------------------------------------------|----------------|

| Supply voltage                                       | 3.3V           |

| Data rate                                            | 3.4GB/s        |

| Tx signal swing(single ended)                        | 400mV to 600mV |

| Single ended high level output voltage $V_H$         | 3.1 V to 3.3 V |

| Single ended low level output voltage V <sub>L</sub> | 2.6 V to 2.9V  |

| Rise time/Fall time                                  | <75ps          |

The phase-locked loop (PLL) circuit used in HDMI applications must have a fast pull-in time and low jitter. Phase locked-loops (PLLs) are widely used to generate well-timed on-chip clocks in high-performance digital systems. For clock generation, since off-chip reference frequencies are limited by the maximum frequency of a crystal frequency reference; a PLL receives the reference clock and multiplies the frequency to the multi-gigahertz operating frequency. The high-frequency clock is then driven to all parts of the chip. Timing recovery pertains to the data communication between chips [4]. The proposed PLL satisfies the HDMI specifications and provides the desired data rate with less jitter, frequencies over wide range and less pull-in time.

The rest of this paper is organized as follows. Section II presents the individual working blocks in proposed PLL. Simulation results of a PLL are given in Section III and the conclusion is given in section IV.

#### 2. PROPOSED PLL BLOCK DIAGRAM

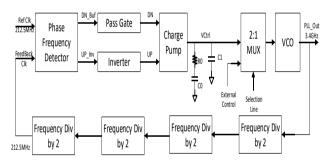

Figure-1. Block diagram of the proposed PLL.

The proposed PLL is composed of mainly six blocks is shown in Figure-1.

- Phase Frequency Detector (PFD)

- Charge Pump (CP) b)

- Low Pass Filter (LPF)

- 3.4 GHz Voltage Controlled Oscillator (VCO) d)

- Divide by N Counter

The advantage of the proposed PLL is by using a 2:1 Multiplexer (Mux) the same design may be used either VCO or complete PLL circuit. If selection line=0, then the circuit perform PLL operation otherwise VCO operation. The 2:1 mux is designed with the pass gate logic so that the design can pass the control voltage without any drop.

#### A. Phase frequency detector (PFD)

PFD produces an error output signal proportional to the phase difference between the phase of the reference clock ( $\Phi_{in}$  (t)) and the generated clock ( $\Phi_{Out}$  (t)). The relationship between the duty cycle of the error signal (V

©2006-2018 Asian Research Publishing Network (ARPN). All rights reserved.

#### www.arpnjournals.com

$_{\rm e}(t)$ ) and the phase difference is linear. The ratio V/rad is defined as the gain of PFD  $(K_D)$ .

$$V_{e}(t) = K_{D}\left[\Phi_{out}(t) - \Phi_{in}(t)\right] \tag{1}$$

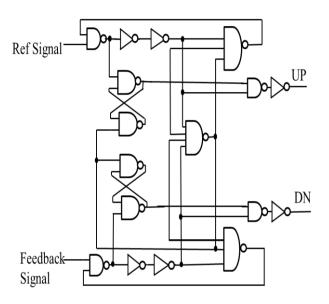

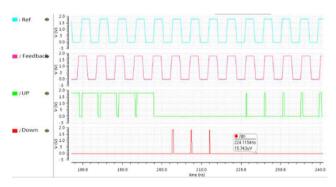

The PFD has 2 inputs namely reference clock and the feedback clock. Up (UP) and Down (DN) signals are its outputs as shown in Figure-2. If there is a phase difference between the two input signals, it generates UP or DN synchronous signals to the charge pump with the duty cycle of the signals proportional to the phase difference between the two input signals [5].

Figure-2. Schematic of a PFD.

Figure-3(a). Output waveform of a PFD.

If the rising edge of the reference clock leads the feedback clock, the UP output of PFD goes high while the DN output remains low. This causes the increase in the frequency of feedback clock. When the feedback clock leads the reference clock, Up remains low and the Down signal goes high till the time equal to phase difference between reference clock and the clock generated. When the loop is in locked state i.e., both the frequency and phase of the reference clock and the clock generated are matched, the output Up and Down signal should remain low. The schematic of PFD is shown in figure 2. The PFD detects the phase difference and produces a pulse on UP

and DN signals. The PFD has been found to work under different process corners. The output waveform of a PFD at typical corner, 1.8V and 27 °C is shown in figure 3(a). When both inputs are rising the outputs of the PFD UP and DOWN signals have overlap with each other, the net current flowing through filter capacitance will be zero. In this way the dead zone of the PFD becomes. Table-2 compares the proposed PFD with recent works [6]-[8]. The proposed PFD consumes low-power. This is lower than previously reported PFD circuits.

**Table-2.** The proposed PFD performance comparison.

| Performance parameter  | [6]   | [7]  | [8]  | This<br>work |

|------------------------|-------|------|------|--------------|

| CMOS tech(µm)          | 0.18  | 0.35 | 0.18 | 0.18         |

| Power supply(V)        | 0.8   | 3.3  | 1.8  | 1.8          |

| Max. freq. (GHz)       | 1     | 2    | 8    | 5.4          |

| Dead-zone              | Free  | Free | Free | Free         |

| Power consumption (mW) | NA    | 4.65 | 0.5  | 0.065        |

| Structure              | Close | Open | Open | Open         |

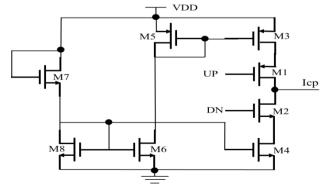

#### B. Proposed normal charge pump

A Charge pump sinks or sources current for a limited period of time depending on the UP and DN signals [6]. UP signal is inverted and passed to Charge pump because the pull up network is controlled by the PMOS transistors. DN signal controls the pull down network. To compensate the delay caused by the inverter for UP signal, the DN signal is passed through a pass gate. The current is the output of charge pump, it will charge or discharge the output capacitor (VCtrl) depending on the UP or DN signals respectively. The schematic of a CP is shown in Figure-4.

When the Up signal is low (pull up network is on) and the Down signal is also low the output capacitance charges through M1 and M3 and the VCtrl rises. Similarly when the Down signal is high (M2 and M4 on) and the Up signal is high (M1 and M3 off) yields a drop in VCtrl since the output capacitance discharges.

Figure-4. Schematic of a proposed normal CP.

VOL. 13, NO. 8, APRIL 2018 ISSN 1819-6608

### ARPN Journal of Engineering and Applied Sciences

©2006-2018 Asian Research Publishing Network (ARPN). All rights reserved.

#### www.arpnjournals.com

The charge pump should be designed in such a way that same current flows through M1 - M4 when both the UP signal and the DN signal is low which should keep the VCtrl constant. Otherwise there will be a charge sharing between the parasitic capacitance on the drains of pull UP and DN networks and the capacitance used in the loop filter causes a static phase error or jitter. When only the M1 and M3 are on the amount of current flowing from Vdd to output capacitance should also be same as the amount of current that flows from output capacitance to ground when only M2 and M4 are on.M5 to M8 transistors act as current source. So the devices should be properly sized in such a way that it obeys the above conditions. Also the jitter should be low for the above sizing. The current mirrors are sized in such a way that they provide sufficient current for the charge pump to produce the required control voltage.

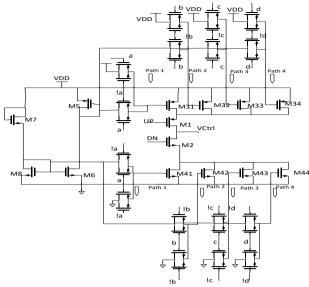

#### B.1 proposed transmission gate charge pump with extra current paths

Figure-5. Schematic of a proposed transmission gate charge pump.

If there is a need to increase the current or reduce the current, the Transmission gate Charge pump is provided with more than one path which is controlled by transmission gate switches is shown in Figure-5. The ON/OFF of these switches determines whether to increase or decrease the current. The sizing of the transistors in each path is done so that the amount of the current doubled from one path to other, so that we can make combinations of different currents to produces stable control voltage and can lock the system quickly. Currents measured in 4 paths are path  $1=65\mu A$ , path  $2=130\mu A$ , path  $3=260\mu A$  and path  $4=520\mu A$ .

**Table-3.** Performance comparison of the proposed charge pump.

| Performance parameter      | [9]       | [10]      | [11]      | [8]       | This work |

|----------------------------|-----------|-----------|-----------|-----------|-----------|

| CMOS Process(µm)           | 0.18      | 0.18      | 0.18      | 0.18      | 0.18      |

| Power supply (V)           | 1.8       | 1.8       | 1.8       | 1.8       | 1.8       |

| Voltage swing              | 0.4-1.2 V | 0.4-1.25V | 0.3-1.58V | 0.25-1.6V | 10nv-1.8V |

| Swing/Vdd (%)              | 44        | 47        | 71        | 75        | 99.9      |

| Constant current magnitude | no        | yes       | yes       | yes       | yes       |

Table-3 compares the proposed charge pump with recent works [8]-[11]. As can be seen, all parameters of the proposed charge pump circuit are improved compared with the other charge pump circuits.

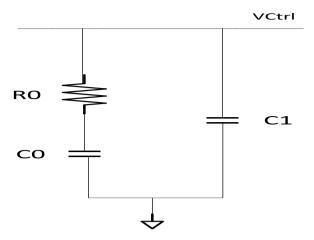

#### C. Loop filter

The output of the PFD consists of a dc component and a high frequency component. But the control voltage of the oscillator must remain quiet in steady state. So by using a passive second order low pass filter (LPF) the high frequency components can be removed and present only the dc level for control voltage (VCtrl). The output of the loop filter is VCtrl .The second order LPF has the smallest resistor thermal noise and

largest capacitor next to the VCO to minimize the impact of VCO input capacitance. The filter also has maximum resistence to variations in VCO gain and charge pump gain. To improve the phase margin and thus stability, minimize the large jump experienced by the control voltage, a second order loop filter is used as shown in Figure-6.

VOL. 13, NO. 8, APRIL 2018 ISSN 1819-6608

## ARPN Journal of Engineering and Applied Sciences

©2006-2018 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

Figure-6. Schematic of a second order loop filter.

The values of R0, C0 and C1 are R0=  $2.5K\Omega$ , C0 = 5pf, C1 = 2.5pf.

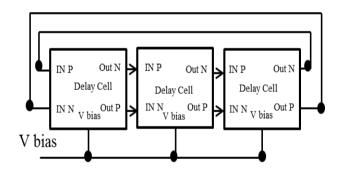

#### D. Voltage controlled oscillator (VCO)

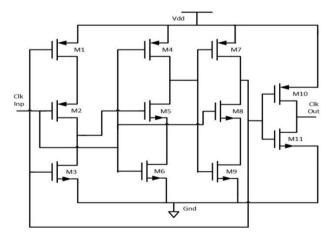

The VCO is an important component in PLL. Conventional VCOs offering many significant advantages have been developed [12]-[20]. Since the output must have low jitter, high linearity and high supply noise rejection. In this application the VCO is designed using differential delay cells in a ring oscillator manner. The VCO has 3 delay cells. The differential delay stage advantage is that, ideally, noise on the supply appears as common-mode on both outputs, and is rejected by next stage in a chain.

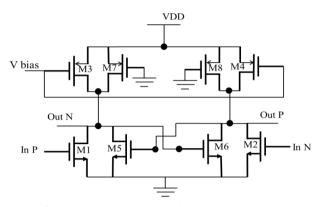

#### **Delay cell**

The schematic of a delay cell is shown in Figure-7. In this figure M1 & M2 NMOS input transistors designed for required gain and bandwidth .M5 & M6 NMOS cross coupled transistors to provide positive feedback. M3 & M4 PMOS transistors serving as current source loads and provide designed current for operating frequency. The current is used by the delay cell to produce output frequencies. First based on the control voltage, the VB will get corresponding voltage to ON the PMOS transistors in Delay cells. Based on the VB, the current driving into the circuit varies and the frequency of the VCO changes. Hence the frequency generation is completely dependent on the current driving through the PMOS network. The operating frequency is nominally controlled by adjusting the PMOS transistors' current. Cross-coupled pairs are adopted to guarantee oscillation with differential outputs. The design is similar to the Lee-Kim delay cell [21]. Unlike the Lee-Kim cell, NMOS transistors are used in the cross-coupled pairs instead of PMOS transistors for a higher operating frequency [22]. The existence of the zero supply sensitivity and the

magnitude of both the positive and negative supply sensitivity depend on the design parameters such as the transistors' width, length, and the P/N size ratio of the delay-cell transistors [23]. The differential delay stage strength is that, ideally, noise on the supply appears as common-mode on both outputs, and rejected by next stage in a chain [24].

Figure-7. Schematic of differential delay cell.

The complete schematic of the 3 stage VCO is shown in Figure-8. The transistor goes from saturation region of operation to triode region of operation if the control voltage crosses 1.15V. So the output frequency of the VCO varies in a nonlinear fashion. In the 3.4GHz range the VCO is linear. The linearity is achieved over a wide-range of frequency from 1.76GHz to 3.4GHz

Figure-8. Schematic of differential ring oscillator.

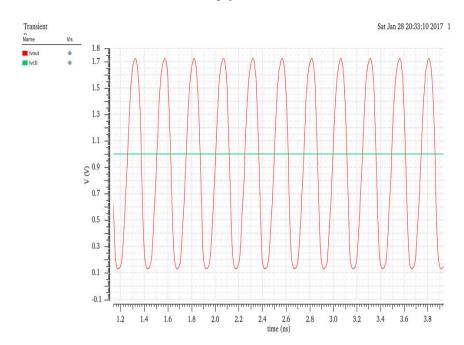

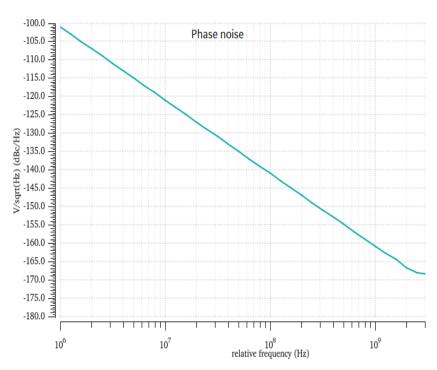

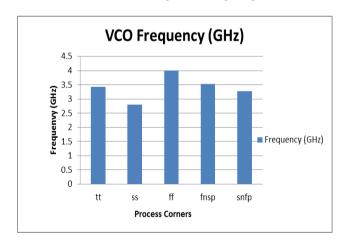

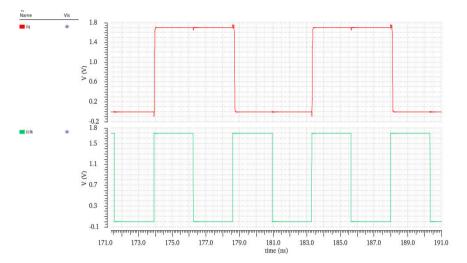

The output wave form of a VCO at typical corner is shown in Figure-9. The output frequency of VCO is 4GHz. The test case is done by giving 1V control voltage and transient analysis is performed. The phase noise of the Proposed VCO is -101dBc/Hz at 1MHz offset is shown in Figure-10(a). Table-4 shows the performance summary of the proposed VCO.

VOL. 13, NO. 8, APRIL 2018 ISSN 1819-6608

# ARPN Journal of Engineering and Applied Sciences ©2006-2018 Asian Research Publishing Network (ARPN). All rights reserved.

**Figure-9.** Output waveform of a VCO.

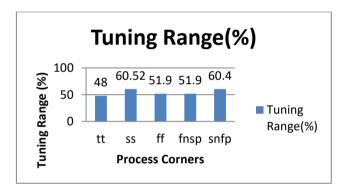

Table-4. Performance summary of proposed VCO.

| VCO parameters/Process corners   | ТТ          | SS         | FF         | FNSP        | SNFP       |

|----------------------------------|-------------|------------|------------|-------------|------------|

| Control voltage (Vctrl) (V)      | 0.9         | 0.9        | 0.9        | 0.9         | 0.9        |

| Frequency (GHz)                  | 3.42        | 2.8        | 4          | 3.52        | 3.28       |

| Linearity (GHz)                  | 1.76 to 3.4 | 1.5 to 3.8 | 2.5 to 5.2 | 2.2 to 4.58 | 1.9 to 4.8 |

| Tuning range(%)                  | 48          | 60.52      | 51.9       | 51.9        | 60.4       |

| output Noise (dBc/Hz)<br>@3.4GHz | -133        | -135       | -132       | -118        | -108       |

| Phase Noise (dBc/Hz)<br>@3.4GHz  | -138        | -140       | -136       | -124        | -116       |

| Supply voltage (V)               | 1.8         | 1.8        | 1.8        | 1.8         | 1.8        |

#### www.arpnjournals.com

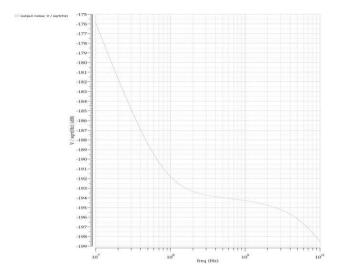

Figure-10(a). Simulated phase noise of the VCO (-101dBc/Hz at 1MHz offset frequency).

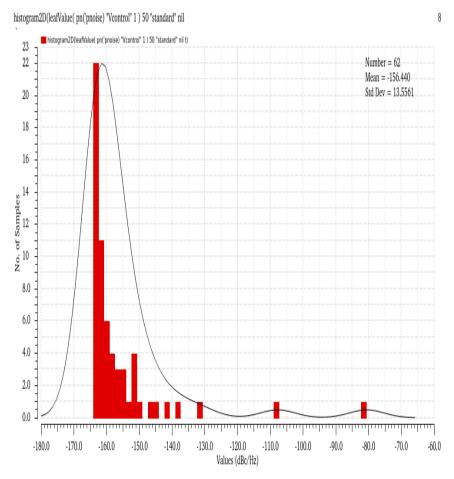

Figure-10(b). Simulated phase noise histogram 2D of phase noise of VCO.

The VCO has been found to work under different process corners. Figure-10(b) shows the histogram 2D of

+phase noise of VCO, from the graph it is observed that mean value of phase noise is -156.44dBc/Hz.

VOL. 13, NO. 8, APRIL 2018 ISSN 1819-6608

## ARPN Journal of Engineering and Applied Sciences

©2006-2018 Asian Research Publishing Network (ARPN). All rights reserved.

#### www.arpnjournals.com

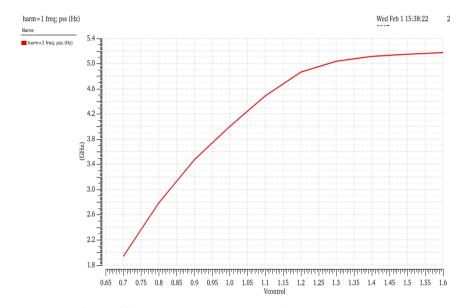

Figure-10(c). Frequency versus control voltage of the VCO.

Figure-10(c) shows the frequency versus control voltage, graph from the graph it is observed that gain of the VCO in the linear region is 3.4GHz/V.

Figure-11 shows the VCO frequency versus different process corners when control voltage is VDD/2 i.e. 0.9V. Figure-12 shows the VCO tuning range versus process corners. It is found that under SS (Slow-slow) corner the VCO achieved highest tuning range.

Figure-11. VCO frequency versus process corners (Control voltage=0.9V).

Figure-12. VCO tuning range (%) versus process corners (Control voltage=0.9V).

#### E. Frequency divider

Frequency divider circuit plays an important role in PLL design [25]-[26]. The T Flip-flop is implemented using D Flipflop. The D-FF is designed using the TSPC [27] so that the 0-0 and 1-1 clock overlaps will not occur.

Figure-13. Schematic of a divide by 2cell. The schematic of a divide by 2 cell is shown in Figure-13. To implement divide by 16 frequency divider

## ARPN Journal of Engineering and Applied Sciences ©2006-2018 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

four T Flip-flops are cascaded together. To avoid race conditions in TSPC, M5 and M6 W/L values should be made larger than M8 and M9. The frequency divider has

been found to work under different process corners. The output waveform of a frequency divider at typical corner, 1.8V and 27  $^{0}$ C is shown in Figure-14.

Figure-14. Output waveform of a frequency divider.

#### 3. PLL ANALYSIS AND RESULTS

#### A. PLL working

PLL ensures that the clock generated tracks the reference clock and then it is said to be locked. If the loop is locked the clock generated and the reference clock has same frequencies but a finite phase difference exists and the PFD generates pulses whose width is equal to constant phase difference. These pulses are filtered to produce the dc voltage (average value) that enables the VCO to operate at a frequency equal to the reference frequency. The constant phase difference is the static phase error.

If the reference frequency is greater than the frequency of clock generated, reference clock accumulates the phase faster and the phase error grows high. So the PFD generates the increasingly wider pulses raising the dc level at the output of the LPF and hence the frequency of VCO increases. The difference in the frequency between the reference clock and the clock generated diminishes. Eventually the width of the PFD output pulses settles to a value. The loop locks only after two conditions are satisfied. One is the frequency of the reference clock and the clock generated are same and the other is the phase difference between them should settle to proper value.

If the output phase error of PLL varies with time, we say the loop is unlocked. Also if the VCO start up frequency is far from the reference frequency, the loop may never lock. The output frequency of PLL can be divided and then feedback. Since we have used the divide by 16 frequency divider at the feedback, we can generate the output of VCO with 16 times the frequency of reference clock. Thus the output of divider stage will be again at the same frequency as the reference clock. So we generate the output frequency which is a multiple of input frequency by a factor of 16. Here the input reference clock period is 4.7058825n (212.5MHz) and a divide by 16 stage is used. So the output frequency of VCO will be

294.117ps (3.4GHz.The block diagram of a proposed PLL is shown in Figure-6.

#### **B. Simulation results of PLL**

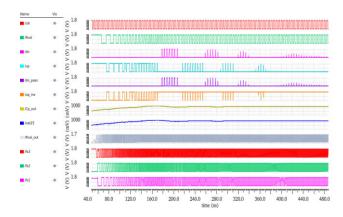

The simulation of each block is done in Cadence Virtuoso. The schematic level design is done using tool Spectre in schematic editor. The layout is done and verified using the tool Assura. The simulation is done in  $1.8V,\ 0.18\ \mu m$  CMOS technology which takes into account the device parasitics. The results of each block is tested for PV conditions. The PLL has been found to work under different process corners and voltage (PV) conditions; the output waveform of PLL at typical corner is shown in Figure-15. PLL can lock from  $2.539\ GHz$  to  $5.0793\ GHZ$  by varying the reference frequency. So the locking range of PLL is  $2.54\ GHz$ .

**Figure-15.** PLL at typical corner (TT) at 27 <sup>o</sup>C, 1.8V.

©2006-2018 Asian Research Publishing Network (ARPN). All rights reserved.

#### www.arpnjournals.com

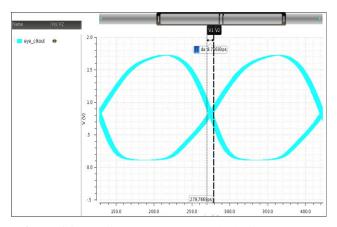

Figure-16. Eye diagram at 3.4 GHz clock (jitter8.78ps).

Jitter is one of the importance performance parameter. Jitter is related to the power of noise of the PLL. The peak to peak jitter is measured for the final 3.4 GHz clock is 8.786 ps as shown in Figure-16. The jitter we observed by the overlapping of 2500 cycles, the calculated RMS jitter is 1.18 ps. The proposed PLL achieves lowest RMS jitter compare to recent works [28] to [34]. The complete PLL block consumes 18.8mW of power from 1.8V supply. PLL-jitter results with power supply variations under typical corner are given in Table-5.

**Table-5.** PLL-Jitter with power supply variations.

| Voltage | Jitter(P-P) in Ps | Jitter(RMS) in Ps |

|---------|-------------------|-------------------|

| 1.7     | 7.060             | 0.948             |

| 1.8     | 8.786             | 1.18              |

| 1.9     | 11.075            | 1.488             |

The commonly used figure of merit (FOM) is described by the following expression.

$$FOM = POWER / FREQUENCY$$

(2)

The proposed design has achieved the lowest FOM of 4.638pJ/Hz.

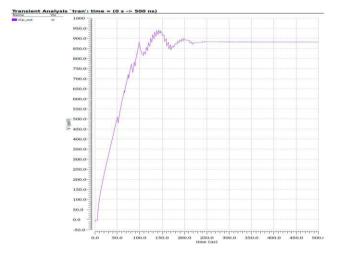

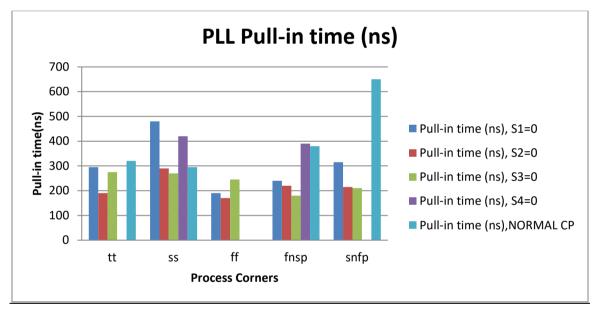

PLL pull-in time is one of the important parameter. Pull-in time is related to the fast-locking of the PLL system. The proposed PLL has been found that it achieves lowest pull-in time i.e. fast-locking system. The simulated pull-in time is shown in Figure-18. Figure-17 shows the PLL output noise with different relative

frequencies. The output noise is -196 V/sqrt(Hz) (dB) at 3.4 GHz.

Figure-17. Simulated output noise for different relative frequencies.

Figure-18. Simulated PLL pull-in time (240ns, Path=1, fnsp).

Table-6 shows the performance comparison of PLLs with prior works [28]-[34] and [8]. The proposed PLL achieved lowest RMS jitter and fast locking time.

## ARPN Journal of Engineering and Applied Sciences

©2006-2018 Asian Research Publishing Network (ARPN). All rights reserved.

#### www.arpnjournals.com

Table-6. PLL performance comparison.

| Performance parameter | [28]     | [29]            | [30]      | [31]      | [32]     | [33]      | [34]      | [8]       | This<br>work |

|-----------------------|----------|-----------------|-----------|-----------|----------|-----------|-----------|-----------|--------------|

| CMOS Process(µm)      | 0.18     | 0.090           | 0.13      | 0.065     | 0.18     | 0.18      | 0.18      | 0.18      | 0.18         |

| Supply voltage (V)    | 0.6      | 0.5             | 0.5       | 1.2       | 1.8      | 1.8       | 1.8       | 1.8       | 1.8          |

| Locking range (GHz)   | 2.4-2.64 | 0.4-2.24        | 0.4-0.433 | 0.06-1.48 | 1.28-1.6 | 0.64-0.8  | 0.5-1.5   | 2.5-7.3   | 1.5-3.8      |

| RMS jitter (Ps)       | NA       | 2.22            | 5.5       | 8.03      | 8.789    | NA        | NA        | 3.21      | 1.18         |

| P-t-P jitter (Ps)     | NA       | 17.89           | 49.1      | 55.6      | 45       | 30        | 24        | 0.35      | 8.786        |

| Locking time          | NA       | NA              | NA        | NA        | NA       | 6 s       | NA        | 0.35µs    | 0.170µs      |

| Power (mW)            | 14.4     | 2.08@2.4G<br>Hz | 0.44      | 4.3       | NA       | 5.14      | 0.32      | 13.4      | 18.4         |

| Results               | Measured | Measured        | Measured  | Measured  | Measured | Simulated | Simulated | Simulated | Simulated    |

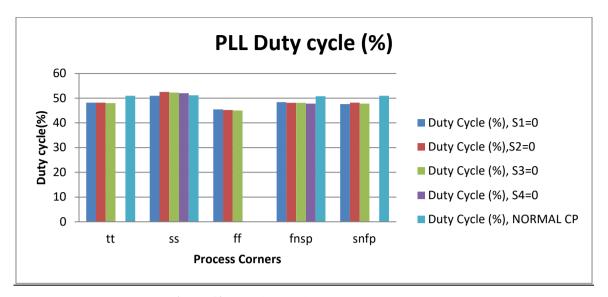

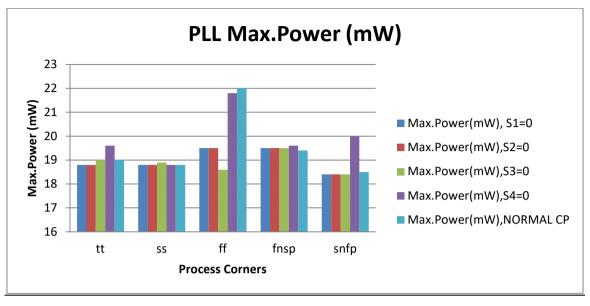

Table-7 shows the Proposed PLL performance with normal charge pump. Tables 8 to 9 shows the proposed PLL performance with proposed Charge pump with transmission gates using path 1 to path 4 respectively. Figures 19 to 21 shows the proposed PLL duty cycle, Pullin time and Max power consumption with different process corners and variation of different current paths in charge pump circuits.

**Table-7.** PLL performance (normal CP).

| PLL parameters/Process corners (Normal CP) | ТТ     | SS     | FF         | FNSP   | SNFP |

|--------------------------------------------|--------|--------|------------|--------|------|

| Control voltage (V)                        | 0.9    | 1      | 0.82       | 0.88   | 0.92 |

| Max. Power (mW)                            | 19     | 18.8   | 22         | 19.4   | 18.5 |

| Pull-in time (ns)                          | 320    | 295    | not locked | 380    | 650  |

| Duty Cycle (%),                            | 51     | 51.2   | vary       | 50.8   | 51   |

| output Noise (dB) @3.4GHz                  | -195.5 | -196.2 | -194.8     | -195.6 | -193 |

| Supply voltage (V)                         | 1.8    | 1.8    | 1.8        | 1.8    | 1.8  |

| CMOS Technology(µm)                        | 0.18   | 0.18   | 0.18       | 0.18   | 0.18 |

**Table-8.** PLL performance (transmission gate CP (path 1)).

| PLL parameters/Process<br>corners (S1=0) | ТТ     | SS     | FF     | FNSP | SNFP   |

|------------------------------------------|--------|--------|--------|------|--------|

| Control voltage(V)                       | 0.9    | 1      | 0.82   | 0.88 | 0.92   |

| Max.Power(mW)                            | 18.8   | 18.8   | 19.5   | 19.5 | 18.4   |

| Pull-in time (ns)                        | 295    | 480    | 190    | 240  | 315    |

| Duty Cycle (%)                           | 48.2   | 51     | 45.5   | 48.4 | 47.6   |

| Max.Current(μA)                          | 190    | 140    | 220    | 200  | 170    |

| output Noise (dB) @3.4GHz                | -195.5 | -196.5 | -194.3 | -195 | -166.4 |

| Supply voltage (V)                       | 1.8    | 1.8    | 1.8    | 1.8  | 1.8    |

VOL. 13, NO. 8, APRIL 2018 ISSN 1819-6608

# ARPN Journal of Engineering and Applied Sciences ©2006-2018 Asian Research Publishing Network (ARPN). All rights reserved.

**Table-9.** PLL performance (transmission gate CP (path 2)).

| PLL parameters/Process<br>corners (S2=0) | ТТ     | SS     | FF     | FNSP   | SNFP |

|------------------------------------------|--------|--------|--------|--------|------|

| Control voltage(V)                       | 0.9    | 1      | 0.82   | 0.88   | 0.92 |

| Max. Power (mW)                          | 18.8   | 18.8   | 19.5   | 19.5   | 18.4 |

| Pull-in time (ns)                        | 190    | 290    | 170    | 220    | 215  |

| Duty Cycle (%)                           | 48.2   | 52.5   | 45.2   | 48.1   | 48.2 |

| Max. Current(μA)                         | 220    | 170    | 270    | 250    | 220  |

| output Noise (dB) @3.4GHz                | -195.5 | -196.3 | -194.7 | -195.2 | -192 |

| Supply voltage (V)                       | 1.8    | 1.8    | 1.8    | 1.8    | 1.8  |

**Table-10.** PLL performance (transmission gate CP (path 3)).

| PLL parameters/Process<br>corners (S3=0) | ТТ     | SS     | FF     | FNSP   | SNFP   |

|------------------------------------------|--------|--------|--------|--------|--------|

| Control voltage(V)                       | 0.9    | 1      | 0.82   | 0.88   | 0.92   |

| Max. Power (mW)                          | 19     | 18.9   | 18.6   | 19.5   | 18.4   |

| Pull-in time (ns)                        | 275    | 270    | 245    | 180    | 210    |

| Duty Cycle (%)                           | 48     | 52.3   | 45     | 48.1   | 47.8   |

| Max. Current(μA)                         | 300    | 220    | 380    | 300    | 280    |

| output Noise (dB) @3.4GHz                | -195.5 | -196.3 | -194.8 | -195.2 | -192.5 |

| Supply voltage (V)                       | 1.8    | 1.8    | 1.8    | 1.8    | 1.8    |

**Table-11.** PLL performance (transmission gate CP (path 4)).

| PLL parameters/Process<br>Corners (S4=0) | TT         | SS     | FF         | FNSP   | SNFP       |

|------------------------------------------|------------|--------|------------|--------|------------|

| Control voltage (V)                      | 0.9        | 1      | 0.82       | 0.88   | 0.92       |

| Max. Power (mW)                          | 19.6       | 18.8   | 21.8       | 19.6   | 20         |

| Pull-in time (ns)                        | not locked | 420    | not locked | 390    | not locked |

| Duty Cycle (%)                           | vary       | 52     | vary       | 47.8   | vary       |

| Max. Current(µA)                         | 430        | 350    | 550        | 450    | 500        |

| output Noise (dB) @3.4GHz                | -195.5     | -166.4 | -194.2     | -195.5 | -166.6     |

| Supply voltage (V)                       | 1.8        | 1.8    | 1.8        | 1.8    | 1.8        |

Figure-19. PLL duty cycle versus process corners.

Figure-20. PLL pull-in time versus process corners.

©2006-2018 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

Figure-21. PLL Max. power versus process corners.

#### 4. CONCLUSIONS

The PLL block is designed to generate 3.4 GHz stable clock with low-jitter for HDMI applications which transfers data at the rate of 3.4 GB/s. All resistances and capacitances were extracted from layout such that we can simulate the circuits more accurately with post layout simulations. The proposed charge pump is designed by using Transmission gates with multiple current paths. By using this method a wide range of current is produced. Therefore a fast Pull-in time (Locking-time) for the PLL is observed. The overall jitter is decreased significantly. The rms jitter of this PLL is 1.18ps at 3.4GHz. The proposed PLL has been found to work under process-voltagetemperature (PVT) conditions (TT-1.8V-27 °C, SS-1.7V-65 °C, FF-1.9V-0 °C). The PLL is simulated with 1.8 V, 0.18µm CMOS process which takes into account the device parasitic and second order effects.

#### REFERENCES

- [1] The Definition Multimedia High Specification version 1.4a, http://www.hdmi.org.

- [2] White Paper on Digital Visual Interface and TMDS Extensions. http://www.siliconimage.com.

- [3] Jinwook Kim; Jeongsik Yang; Sangjin Byun; Hyunduk Jun; Jeongkyu Park; Conroy, C. S G; Beomsup Kim. 2005. A four-channel 3.125-Gb/s/ch CMOS serial-link transceiver with a mixed-mode adaptive equalizer. Solid-State Circuits, IEEE Journal of. 40(2): 462-471.

- [4] Behzad. Razavi. 2002. Design of Analog CMOS Integrated Circuits. Tata McGraw -hill Edition. pp. 550-568.

- [5] Ramanjaneyulu Ningampalli, Satyanarayana Donti and Satyaprasad Kodati. 2015. Design of PFD, CP and FD circuits for 3.4 GHz PLL using 0.18µm CMOS Technology. International Journal of Applied Engineering Research (IJAER). 10(14): 34490-34496.

- [6] Kailuke AC, Agrawal P, Kshirsagar RV. 2014. Design of phase frequency detector and charge pump for low voltage high frequency PLL. In: International conference on electronic systems, signal processing and computing technologies (ICESC). pp. 74-8.

- [7] Babazadeh H, Esmaili A, Hadidi K. 2009. A highspeed and wide detectable frequency range phase detector For DLLs. NORCHIP. 1-3.

- [8] Erfani-Jazi HR, Ghaderi N. 2015. A divider-less, high speed and wide locking range phase locked loop. Int. J Electron Commun. (AEU). AEUE5.136, 1-8.

- [9] Huili X, Zhiqun L. 2012. Design of a low power charge pump circuit for phase- locked loops. In: High speed intelligent communication forum (HSIC). pp. 1-4.

- [10] Hati M, Bhattacharyya T. 2013. A high o/p resistance, wide swing and perfect cur- rent matching charge having switching circuit for PLL. Microelectronics J. 44: 649-57.

- [11] Erfani Jazi HR, Ghaderi N. 2014. A novel bulk driven charge pumps for low power, low voltage applications. IEICE Electron Express. 11: 1-7.

## ARPN Journal of Engineering and Applied Sciences

©2006-2018 Asian Research Publishing Network (ARPN). All rights reserved.

- [12] Jun-Chau Chien and Liang-Hung Lu. 2007. Design of wide-tuning-range millimeter-wave CMOS VCO with a standing-wave architecture. IEEE J. Solid-State Circuits, 42(9): 1942-1952.

- [13] Young-Jin Moon, Yong-Seong Roh, Chan-Young Jeong and Changsik Yoo. 2009. A 4.39-5.26 GHz LC-tank CMOS voltage-controlled oscillator with small VCO-gain variation. IEEE Microw. Wireless Compon. Lett. 19(8): 524-526.

- [14] Jian-An Hou and Yeong-Her Wang. 2009. A 5 GHz differential colpitts CMOS VCO using the bottom PMOS cross-coupled current source. IEEE Microw. Wireless Compon. Lett. 19(6): 401-403.

- [15] José Luis González, Franck Badets, Baudouin Martineau, and Didier Belot. 2010. A 56-GHz LCtank VCO with 17% tuning range in 65-nm bulk CMOS for wireless HDMI. IEEE Trans. Microw. Theory Techn. 58(5): 1359-1366.

- [16] Meng-Ting Hsu and Po-Hung Chen. 2011. 5G Hz low power CMOS LC VCO for IEEE 802.11a application. in Proc. Asia-Pacific Microw. Conf. pp. 263-266.

- [17] Zuow-Zun Chen and Tai-Cheng Lee. 2011. The design and analysis of dual-delay-path oscillators. IEEE Trans Circuits Syat. I. 58(3): 470-478.

- [18] Pei-Kang Tsai and Tzuen-His Huang. Integration of current-reused VCO and frequency tripler for 24-GHz low-power phase-locked loop applications. IEEE Trans. Circuits Syst. II, Exp. Briefs. 59(4): 199-203.

- [19] Qiyang Wu, Salma Elabd, Tony K. Quach, Aji Mattamana, Steve R. Dooley, Jamin McCue, Pompei L. Orlando, Gregory L. Creech and Waleed Khalil. 2013. A-189 dBc/Hz FOMT wide tuning range Kaband VCO using tunable negative capacitance and inductance redistribution. in Proc. IEEE Radio Freq. Integr. Circuits (RFIC) Symp. pp. 199-202.

- [20] Heein Yoon, Yongsun Lee, Jae Joon Kim, and Jaehyouk Choi. 2014. A wideband dual-mode LC-VCO with a switchable gate-biased active core. IEEE Trans. Circuits Syst. II, Exp. Briefs. 61(5): 289-293.

- [21] Lee. J and Kim. B. 2002. A low-noise fast-lock Phase-Locked Loop with adaptive bandwidth control. in IEEE Journal of Solid-state circuits. 35: 1137-1145.

- [22] Behzad Razavi, Kwing F. Lee and Ran H. Yan. 1995. Design of high speed, low power frequency dividers and phase-locked-loops in deep submicron CMOS. IEEE J. Solid-State Circuits. 30(2): 101-109.

- [23] Ping-hsuan Hsieh, Jay Maxey and Chih-kong Ken Yang. 2009. Minimizing the supply sensitivity of a CMOS ring oscillator through jointly biasing the supply and control voltages. IEEE J. Solid-State Circuits. 44(9): 2488-2495.

- [24] Ramanjaneyulu N., Satyanarayana D., Satya Prasad K. 2017. Design of a 3.4 GHz Wide-Tuning-Range VCO in 0.18 µm CMOS. Lecture Notes in Networks and Systems. 5: 227-234, Springer, Singapore. DOI: 10.1007/978-981-10-3226-4 22.

- [25] Wenrui Zhu, Haigang Yang, Tongqiang Gao, Fei Liu, Tao Yin, Dandan Zhang and Hongfeng Zhang. 2015. A 5.8-GHz Wideband TSPC Divide-by-16/17 Dual Modulus Prescaler. IEEE Trans. VLSI Systems. 23(1): 194-197.

- [26] Wu-Hsin Chen and Byunghoo Jung. 2011. Highspeed low-power true single-phase clock dualmodulus prescalers. IEEE Trans. Circuits Syst. II, Exp. Briefs. 58(3): 144-148.

- [27] [27] J. M. Rabaey, A. Chandrakasan, and B. Nikolic. 2003. Digital Integrated Circuits: A Design Perspective. 2<sup>nd</sup> ed. New York, NY, USA: Prentice-Hall. pp. 350-352.

- [28] Chung-Ting Lu, Hsieh-Hung Hsieh and Liang-Hung Lu. 2010. A low-power quadrature VCO and its application to a 0.6-V 2.4-GHz PLL. IEEE Trans. Circuits Syst. I, Reg. Papers. 57(4): 793-802.

- [29] Kuo-Hsing Cheng, Yu-Chang Tsai, Yu-Lung Lo and Jing-Shiuan Huang. 2011. A 0.5-V 0.4-2.24-GHz inductor less phase-locked loop in a system-on-chip. IEEE Trans. Circuits Syst. I. 58(5): 849-859.

- [30] Wu-Hsin Chen, Wing-Fai Loke, and Byunghoo Jung. 2012. A 0.5-V, 440µW Frequency synthesizer for implantable Medical Devices. IEEE journal of solid-State Circuits. 47(8): 1896-1907.

- [31] I-Ting Lee, Yun-Ta Tsai, and Shen-Iuan Liu. 2013. A Wide-Range PLL using Self-Healing Prescaler /VCO in 65-nm CMOS. IEEE Trans. VLSI Systems. 21(2): 250-258.

VOL. 13, NO. 8, APRIL 2018 ISSN 1819-6608

## ARPN Journal of Engineering and Applied Sciences ©2006-2018 Asian Research Publishing Network (ARPN). All rights reserved.

- [32] Chung-Yi Li, Chung-Len Lee, Ming-Hong Hu, and Hwai-Pwu Chou. 2014. A Fast Locking-in and Low Jitter PLL with a Process Immune Locking-in Monotor. IEEE Trans. VLSI Systems. 22(10): 2216-2220.

- [33] Singh G, Singh D, Moorthi S. 2012. Low power low jitter phase locked loop for high speed clock generation. In: Asia pacific conference on postgraduate research in microelectronics and electronics (PrimeAsia). pp. 192-6.

- [34] Aditya S, Moorthi S. 2013. A low jitter wide tuning range phase locked loop with low power consumption in 180 nm CMOS technology. In: IEEE Asia Pacific conference on postgraduate research in microelectronics and electronics (PrimeAsia). pp. 228-32.