## ARPN Journal of Engineering and Applied Sciences

©2006-2018 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

## NEW SWITCHING TECHNIQUE FOR THE MODIFIED CASCADE FIVE LEVELS INVERTER

Mustafa F. Mohammed<sup>1</sup>, Ali H. Ahmad<sup>2</sup> and Abdulrahim Thiab Humod<sup>2</sup> <sup>1</sup>University of Information Technology and Communications, Baghdad, Iraq <sup>2</sup>Electrical Engineering Department, University of Technology, Baghdad, Iraq E-Mail: mfmfzy@yahoo.com

#### ABSTRACT

In inverters design, the reduction in a number of switches and making the switching frequency at the fundamental frequency are good techniques for increasing the efficiency of single-phase inverters. In this paper, there is a new switching technique used for the modified cascade five levels inverter based on single pulse width modulation PWM method. A comparison is made by using of single PWM between the five levels and the three levels inverter (full bridge inverter). The shifting angles and its time equivalent relationships are derived. The single PWM method showed that, at a particular trend of harmonic elimination which is the 5<sup>th</sup> harmonic, lower total harmonic distortion percentage THD % can be achieved. All the simulations are made by using of MATLAB SIMULINK R2015a.

Keywords: inverter, multi-levels, single PWM, modified cascade.

#### 1. INTRODUCTION

In last three decades, multi-levels inverters get more attention than the traditional three level inverters. Since, it has lower total harmonic distortion percentage THD, more efficiency, and less dependency on filters. Cascade multi-levels inverters have simple construction and control. It is easily working at the fundamental frequency or by using one of the modulation methods that need a carrier with a relatively high frequency. THD can be low if more cascade H bridges are added. But, more adding results in a reduction in efficiency due to more conduction and switching losses of the used switches. There was a new design is made by [1-2], with Selective Harmonic Elimination SHE method. This design is made with a reduction in a number of switching devices of cascade H- bridge multi-levels inverter. The construction contains single H-bridge and, for each separate DC source one extra switch can be added i.e. for seven levels, it contains three DC sources with 7 IGBT switches and with five levels, only six switches are needed. The SHE is a good method to detect the angles that eliminate the particular harmonics. But, it needs to apply numerical analysis methods and or artificial intelligence methods to detect these angles. In the work that was made by Kannan Ramani et al[3], a new symmetric cascade H-bridge multilevels inverter is made with reduction switching components at each level. It connects switches in series and parallel to each separated DC source thus, it makes the inverter has more complex design when the number of levels are increased. There is a comparison of THD in three levels and cascade H-bridge inverter is made in [4]. This comparison is with the traditional three phase six switches inverter where low THD was gotten by using of five levels cascade-bridge inverter. Each type of inverters sometimes needs a modulation technique for the switching scheme to get lower THD. One of these techniques is single pulse width modulation [5]. This method eliminates a particular nth harmonic by a suitable shifting angle if it is used with the traditional H-bridge three levels inverter. Also, in this method the switching frequency is made same

as the fundamental frequency thus, the switching losses will decrease and efficiency will increase. This paper introduces a new switching technique for a modified cascade five levels inverter with a comparative study between this inverter and a traditional three levels inverter [2], by using single pulse modulation method and showing its impact in decreasing the THD.

### 2. RELATION BETWEEN TIME AND PARTICULAR ANGLE IN A SINE WAVE

In the electrical system, the sine wave can be represented by degrees or radian systems. It also can be represented by time in seconds. Irrespective of the frequency used, the single sine wave can be represented by 360° and the half of this wave is equal to 180°. In inverters design, the switching time among the switching devices should be known to make the suitable angles that make a proper working of the inverter at different loading conditions. Some Inverters contains microcontrollers to make the switching angles. These angles may be represented by its time equivalent. In this paper, there is a method to find the equivalent time to a particular angle  $(\phi^0)$  in the sine wave as follows:

$$F = \frac{1}{T} \tag{1}$$

Where F is the frequency and T is the period of a frequency.

Since T = 360° then

$$\frac{T}{2} = 180°$$

or  $180° = \frac{1}{\frac{1}{2F}}$

At any angle  $\Phi^0$ , the equivalent time =  $T_a$

$$\frac{180^0}{\frac{1}{2F}} = \frac{\phi^0}{T_q} \tag{2}$$

©2006-2018 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

Then

$$\phi^0 = 180^0 \times T_q \times 2F \tag{3}$$

And

$$T_q = \frac{\phi^0}{180^0 \times 2 \times F} \tag{4}$$

### 3. SINGLE PULSE WIDTH MODULATION OF A THREE LEVELS INVERTER

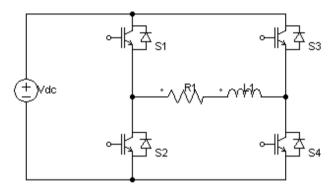

Figure-1 represents the three levels inverter, where these levels are (Vdc, 0, and - Vdc). This inverter contains 4 switching devices named as (S1, S2, S3, and S4).

Figure-1. Three levels inverter.

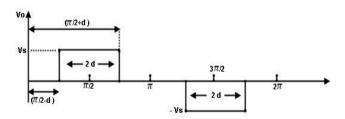

One of the switching methods of this inverter is "single pulse width modulation". For the single pulse modulation, a pulse is made at each half cycle of the output voltage as shown in Figure-2. The width of the pulse is 2d and this pulse is shifted from the origin by a duration of  $(\frac{\pi}{2} - d)$ . The shape of the output voltage is called quasi-square wave.

From the Fourier analysis of Figure-2 [6]:

$$a_n = 0 (5)$$

$$b_n = \frac{2}{\pi} \int_{\left(\frac{\pi}{2} - d\right)}^{\left(\frac{\pi}{2} + d\right)} \sin n\omega t \ d(\omega t)$$

(6)

**Figure-2.**Single pulse modulation method.

$$b_n = \frac{4V_s}{n\pi} \left[ \sin \frac{n\pi}{2} \sin nd \right] \tag{7}$$

So the instantaneous output voltage is:

$$V_o = \sum_{n=1,3,5}^{\infty} \frac{4V_s}{n\pi} \sin \frac{n\pi}{2} \sin nd \sin nwt$$

(8)

If *nd* is made equal to  $\pi$  or  $d = \frac{\pi}{n}$ , equation (8) shows that the nth harmonic is eliminated from the inverter's output voltage. Since d is the duration of the pulse and it is required to find the angle  $\phi^0$  that make the nth harmonic to be zero then:

$$\phi^0 = \frac{\frac{\pi}{2}}{n} \text{ or } n = \frac{\frac{\pi}{2}}{\phi^0}$$

(9)

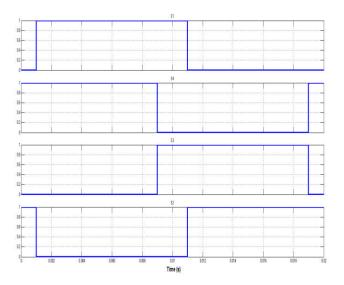

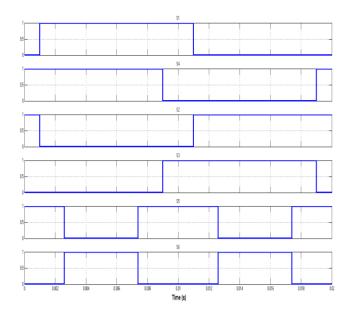

The switching strategy is made as follows and shown in Figure-3.

- For first  $180^{\circ}$ , S1 is shifted forward by angle  $\phi^{\circ}$  and S4 is shifted backward by angle  $\phi^0$ .

- For the second half wave S2 is the inverse (NOT) of S1 and S3 is the inverse of S4.

The nth harmonic can be eliminated by the shifting angle  $\phi^0$ .

Figure-3. Switching signals of a three levels inverter.

## 4. SINGLE PULSE WIDTH MODULATION OF A MODIFIED FIVE LEVELS CASCADE **INVERTER**

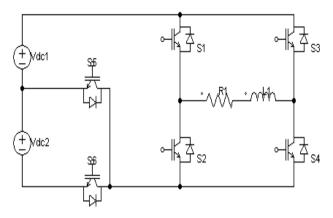

The topology of a modified cascade five levels inverter contains 6 switches named as (S1, to S6) as shown

©2006-2018 Asian Research Publishing Network (ARPN). All rights reserved.

#### www.arpnjournals.com

in Figure-4. The output voltage levels are five as (Vdc1, Vdc1+VDdc, 0, -Vdc1, and -Vdc1-Vdc2).

Figure-4. Modified cascade five levels inverter.

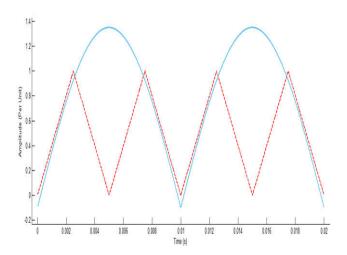

The inverter contains three levels H-bridge inverter as a portion of it and two switching devices which are S5 and S6 with two separate DC sources. The switching scheme of the portion of H-bridge circuit is the same as in the three levels inverter above. The only remaining are switches S5 and S6. The switching of these two IGBT devises can be made by a comparison between an absolute sine wave as a modulating or reference signal with a triangle carrier wave. The frequency of this carrier is double of the fundamental frequency as shown in Figure-5. The switching signals for all of the 6 switching devices are as shown in Figure-6, where S5 is ON when the modulation signal ≥ carrier signal and S6 is S5 inverse.

Figure-5. Modulating and carrier signals for switches S5 and S6.

Figure-6. Switching signals of the proposed five levels inverter.

#### 5. SIMULATION RESULTS

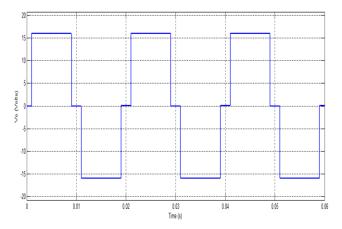

According to the switching scheme of Figure-3, the three levels inverter is simulated. By taking different shifting angles  $\phi^0$  in forward and backward as shown in Table-1, where its equivalent time  $T_q$  at each angle  $\phi^0$ , the THD is calculated. The output voltage is as shown in Figure-7.

**Table-1.**THD % at each shifting angle or equivalent time of the three levels inverter.

| n  | $\phi^0$ | Time $T_q$ (s)          | THD     |

|----|----------|-------------------------|---------|

| 3  | 30       | $1.667 \times 10^{-3}$  | 31.09 % |

| 5  | 18       | $1 \times 10^{-3}$      | 30.19 % |

| 7  | 12.85    | $17.138 \times 10^{-4}$ | 33.58 % |

| 9  | 10       | $5.556 \times 10^{-4}$  | 36.12 % |

| 11 | 8.18     | $4.544 \times 10^{-4}$  | 38.08 % |

Figure-7. Output voltage of the three levels inverter.

©2006-2018 Asian Research Publishing Network (ARPN). All rights reserved.

#### www.arpnjournals.com

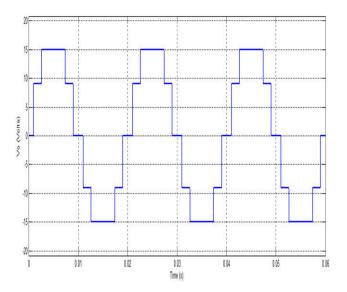

The five levels of the modified cascade inverter is also simulated. According to the switching scheme of the Figure-6, the resulted output voltage is as shown in Figure-8.

Figure-8. Output voltage of the five levels modified cascade inverter.

In this inverter type, the switching signals of switches S5 and S6 are fixed at its maximum value. The change is made only by the shifting angle  $\phi^0$  for making the single pulse width modulation technique at ±Vdc1 levels. By shifting in forward and backward, delay angle  $\phi^0$ ,  $T_q$ , and THD are calculated as shown in the Table-2. The particular angle  $\phi^0$  and time  $T_a$  are calculated by using equations (3 & 4) respectively.

Table-2. THD at each delay angle or equivalent time of the five levels inverter.

| n  | $\phi^0$ | Time $T_q$ (s)          | THD     |

|----|----------|-------------------------|---------|

| 3  | 30       | $1.667 \times 10^{-3}$  | 26.91 % |

| 5  | 18       | $1 \times 10^{-3}$      | 17.24 % |

| 7  | 12.85    | $17.138 \times 10^{-4}$ | 17.36 % |

| 9  | 10       | $5.556 \times 10^{-4}$  | 18.66 % |

| 11 | 8.18     | $4.544 \times 10^{-4}$  | 19.94 % |

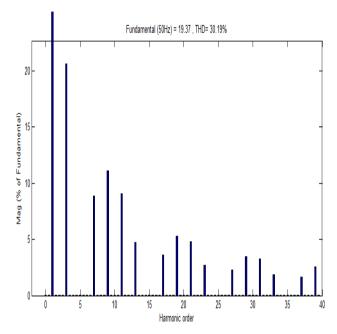

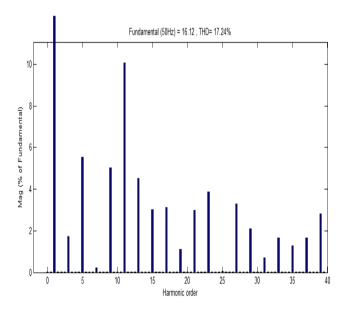

From Tables (1 & 2), it is found that when nth harmonic equals to 5, lower THD% can be achieved. In three levels inverter it eliminates all the odd quintuple harmonics like (5<sup>th</sup>, 15<sup>th</sup>, 25<sup>th</sup>... etc.) as shown in Figure-9. Also, in the proposed five levels inverter it eliminates (7<sup>th</sup>& 25<sup>th</sup>) harmonics and reduces (3<sup>rd</sup>, 5<sup>th</sup> ...etc.) and the only drawback here in increasing the 11<sup>th</sup> harmonic content as shown in Figure-10.

Figure-9. Output voltages' THD% of the three levels inverter.

Figure-10. Output voltage's THD% of the five levels inverter.

#### 6. CONCLUSIONS

In this paper, the simulations of the three levels inverter and the proposed modified cascade five levels inverter are made successfully. A relation between the delay angle in degree and time in seconds of a sine wave is explained in details. By using the single pulse modulation method, low THD can be achieved at both types of inverters. When the shifting angle is made 18<sup>0</sup>, lower THD can be gotten. The only drawback is made at the 11th harmonic in the proposed five levels inverter. Thus, it can be concluded that the proposed five levels inverter is good for applications up to 2 kW or a suitable small LC filter VOL. 13, NO. 14, JULY 2018 ISSN 1819-6608

# ARPN Journal of Engineering and Applied Sciences

©2006-2018 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

can be made to remove the impact of this harmonic and get lower THD.

#### REFERENCES

- [1] K. Gobinath, S. Mahendran, and Dr. I. Gnanambal. 2013. Novel Cascaded H-Bridge Multilevel Inverter with Harmonics Elimination. Proceedings of 2013 International Conference on Green High Performance Computing. IEEE.

- [2] Gobinath K., Mahendran S. and Gnanamba I. 2013. New Cascaded H-Bridge Multilevel Inverter with Improved Efficiency. International Journal of Advanced Research in Electrical Electronics and Instrumentation Engineering (IJAREEIE). 4(2): 1263-1271.

- [3] Kannan Ramani, Mohd Ali, Jagabar Sathik, and Selvam Sivakumar. 2015. A New Symmetric Multilevel Inverter Topology Using Single and Double Source Sub-Multilevel Inverters. Journal of Power Electronics. 15(1): 96-105.

- [4] Rajesh B. and Dr. Manjesh. 2016. Comparison of Harmonics and THD Suppression with Three and 5 Levels Multilevel Inverter-Cascaded H bridge. 2016 International Conference on Circuit, Power and Computing Technologies. IEEE.

- [5] Muhammed H. Rashid. 2007. Power Electronics Circuits Devices and Applications. 3<sup>rd</sup> edition. Pearson Education Inc. second impression. pp. 248-250.

- [6] Dr. P.S. Bimbhra. 2010. Power Electronics. 4<sup>th</sup> edition, Khanna Publishers. 15th reprint. pp. 455-456.