# DESIGN AND IMPLEMENTATION OF EMBEDDED OBSTACLE AVOIDANCE SYSTEM ON FPGA

Noor Aldeen A. Khalid and Muataz H. Salih

School of Computer and Communication Engineering, Universiti Malaysia Perlis (UniMAP) Perlis, Malaysia E-Mail: nooraldeen4561@gmail.com

# ABSTRACT

The implementation of obstacle avoidance system is important application for robotics and in generally is most part used in many applications such as, security or military. This project applied by utilized FPGA platform (DE0-nano Board). The robot can distinguish the obstacle by using ultrasonic sensor (HRLV-MaxSonar). Perception approach and motion planning is the most basic part in this project. Ultrasonic was utilized to detect any obstacle while, the DE0-Nano board is the project platform and the characteristic of FPGA offer programmability and makes it easier to implement on different mobile robot platforms. The Sensor was integrated with the DE0-Nano board. In this project a structure VHDL coding is utilized for design the obstacle avoidance and Quartus II 13.0sp1 as a development CAD tool. The implementation of complex obstacle avoidance with FPGA platform (DE0-Nano) is possible because of the rich logic elements. A specific sensor characteristics testing was carried and robot stability to master these sensor and robot. The result for our project that already got shown the frequency for DE0-nano achieved up to 1.3 GHz, also the total logic elements was used for this project is 4,042 and shown the result for ultrasonic sensor is a high precision and higher accuracy for detection the obstacle and avoids it.

Keywords: embedded system, obstacle avoidance system, FPGA design.

## INTRODUCTION

The FPGA platform is the most appropriate choice while implementing obstacle avoidance system. One of the basic characteristics of the FPGA platform is that, it helps in multiple programming and implemented on several mobile robot platforms with very few modification and no hardware rewiring. Besides, it is possible to use the DE0 Nano board on any of the robot platforms because of its compact size. In our project the ultrasonic sensors can successfully and easily to avoid obstacles. The VHDL is used as the FPGA design. By using the ultrasonic sensor the robot is able to resolve the obstacle detection issue, and the DE0 Nano board was selected for mastering all sensors and controlling the robot motors through L293D chip to let the robot moved in different directions.

The DE0 Nano refers to a compact-sized FPGA development platform; which is more suited for the portable designing projects like a robot. The configurable logic block used in the FPGA helps in updating the design easily. Also, the DE0 Nano platform consists of rich I/O pins, and enables it to simultaneously handle huge data volume and achieve higher data processing speeds with frequency up to 1.3GHz. The DE0 Nano platform solves the problems related to a low processing speed and I/O and resource limitation. The DE0 Nano platform was interfaced with the sensor and the robot. Thereafter, the VHDL used for overcoming the design-based challenges. The Quartus II 13.0sp1 CAD tool software acted as the designing tool for simulating the VHDL coding or the block diagram for validating the performance of this design

## **RELATED WORK**

FPGA is very popular in all of the application domains. Initially, the FPGAs were used in the form of the

digital glue logic or only for prototyping, however, today; they are generally applied as integral components of communications, consumer designs like complex electronics, space systems and military. The FPGAs are becoming very popular not only due to a decreasing performance gap between the ASICs and the FPGAs but also due to better reconfiguration flexibility of the system that helps in product development, its maintenance and obtaining updates. They are one of the best and most popular hardware platforms for implementing and testing the digital designs and are regularly used by the educators and circuit designers. Furthermore, they are also used by the people who contribute towards the online design resources like Open source, who assess and justify their open source designs using the different FPGA chips. The validation and testing of designs using the FPGA chips improves the confidence and the product credibility of the design resources[1].

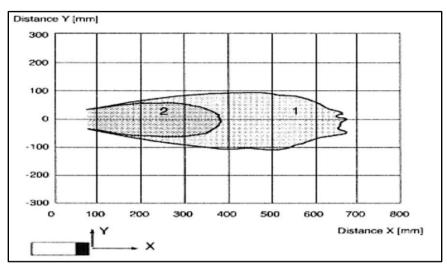

US sensors are very popular for measuring distances and are a reliable source for obstacle detection. As they do not need any vision, they can be used under poor lighting and for transparent objects. However, all US sensors have a limitation because of their sensitivity to the specular surfaces, wide beam-width, and their inability to distinguish objects present at a distance of 0.5 m. Due to the specific specular nature of the reflections from the US wave, the reflecting objects, which seem normal at the sensor acoustic axis, can be detected successfully. Hence, the objects have to possess a >1 cm precision in the distance measurement of around 6 m. However, one of the most accurate methods for determining the object distance is the Time of Flight (TOF) measurement. Figure-1 presented the target response curve of the US sensors for flat surfaces and rounded bars.

Ó

Figure-1. Target Response Curves of the US sensor Curve. [2]

#### **COMPARISON BETWEEN PLATFORMS**

The FPGAs are integrated circuits that can be customised by the user for implementing arbitrary digital functions. The modem FPGAs can combine the general logic resources with the microprocessors, programmable interconnections, multipliers, networking, memories, the delay/phase locked loops and such other cores for designing a more versatile System on Chip (SoC). Table 1shown the comparison between platforms.

| Platform                  | Adv.                                                                                                                                                                                                                                                 | Dis.                                                                                                                                                                                | Program.<br>Language |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| FPGA                      | True parallel nature.<br>Reconfigurable.<br>Best suited for real time application.<br>Flexible functionality.<br>FPGA can be re-programmed in the field<br>to fix bugs.<br>High logic density.<br>Obsolescence protection.<br>Fast in time to market | High power consumption.<br>Expensive.<br>Limited size options.                                                                                                                      | VHDL<br>Verilog      |

| ASIC                      | Low power consumption.                                                                                                                                                                                                                               | Increasing IC design costs<br>Don't provide flexible programma-bility.                                                                                                              | BASIC,<br>GW-BASIC   |

| TNETV3020<br>DSP platform | Low power consumption.<br>Low cost.<br>Hard real time processing.                                                                                                                                                                                    | The clock rate limits theperformance.<br>Debugging and visibility challenges.<br>Fixed design not reconfigurable.<br>Very challenging in programming.<br>General purpose processor. | C<br>Assembly        |

| SBC                       | Low power consumption.<br>Low cost.<br>High computational performance                                                                                                                                                                                | Not customizable.<br>Fixed design not reconfigurable.                                                                                                                               | С                    |

| CPLD                      | Low power consumption.<br>Low cost.<br>Programmable.<br>High speed                                                                                                                                                                                   | High power consumption.<br>Limited no. of blocks.<br>Much less resources than FPGA.                                                                                                 | VHDL, Verilog        |

Table-1. Comparison of Embedded Platforms [3].

## METHODOLOGY

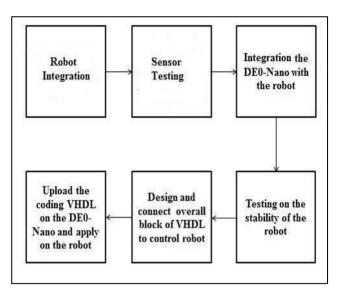

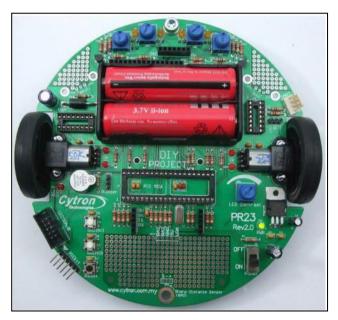

The installation was started with the DIY (Do It Yourself) PR23 mobile robot and then, interfacing the robot with sensor. Here, the aim was to control on the sensor with the robot and measuring the data using the sensor also testing the sensor features. After collecting all the data, the next step involved the integration of the DE0 Nano board with the sensor and then the stability of the overall mobile robot platform was tested. The control algorithm evolved in Quartus II 13.0sp1. Finally, the DE0 Nano was implemented as the effective robot platform. The overall project flow was shown in Figure-2; while Figure-3 describes the PR23 Mobile Robot Platform.

Figure-2. Overall Flow of the Project.

Figure-3. PR23 Mobile Robot Platform (www.cytron.com.my, 2009).

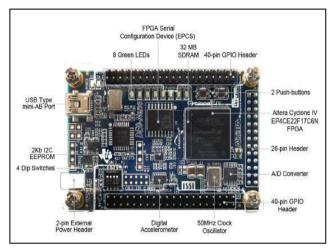

The DE0-Nano platform was implemented in many robots. Some of the features of this platform include an Altera Cyclone IV FPGA (having 22,320 logic elements), 2 Kb EEPROM, 32 MB SDRAM, and 64 Mb of a serial layout memory device along with the processor of 1.3 GHz. For attaching actual detectors, the DE0-Nano Board includes an 8-channel semiconductor with a 12-bit Analogue-to-digital converter also contains 13-bit Analogue Devices and a 3-axis (X, Y, Z) accelerometer device.

The DE0-Nano Board consists of a built-in USB Blaster for the programming of the FPGA platform, and the board can be turned on using an USB port or an external power source. The board also consists of developed headers which use many Terasic family cards or such similar appliances like engines and motors. The input and the output ports include 2 push-buttons, 8 user LEDs and 4 dip-switches [4]. The DE0 Nano board described in Figure-3.

Figure-4. The top view of the DE0-Nano Board [4].

HRLV-MaxSonar (Ultrasonic sensor) was used and the main principle of the sensor is that the sensor transfers a pack of reflective sound beams and determines the time interval that occurs between the sending of the signal and receiving of the echo. This echo signal is collected from different measuring angles as the sensor sends a divergent signal. Figure-5 shows the design of the HRLV-MaxSonar sensor.

Figure-5. HRLV-MaxSonar ultrasonic.

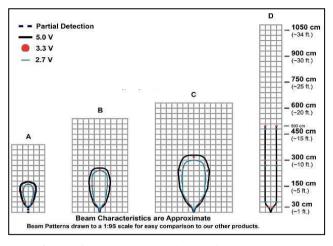

The output values in 3 formats (UART, PWM, and analogue) were obtained. The sensor requires 5V for detecting a far object. Also the certain tests for determining the accuracy of the measurements of this sensor were carried out. In Figure-6 shown the characteristics and the beam pattern of the ultrasonic sensor.

Figure-6. Beam Characteristics of the Ultrasonic Sensor[5].

#### Testing and determining the sensor characteristics

Here, an oscilloscope for gathering all the information from the sensor was used. However, the light and the colour of the reflecting object significantly affected the sensor reading. Hence, objects with different colours and sizes for decreasing the error and obtaining the accurate results were selected.

### MOTOR CONTROLLING

For controlling the direction of the motor, a VHDL block was generated. Any disparity noted in the output values of the L293D chip allowed the robot to move in a completely new direction. The L293D consisted of 2-H bridge driver circuits for controlling the 2 DC motors and also simultaneously functioning. Out of the 16 L293D chip pins, the 2 and 7 pair, and the 10 and 15 pin pair were used for controlling the motor operation. An input of 00 or 11 stopped the movement of the respective motor, while an input value of 01 and 10 helped in rotating the motor either in a clockwise or an anticlockwise direction.

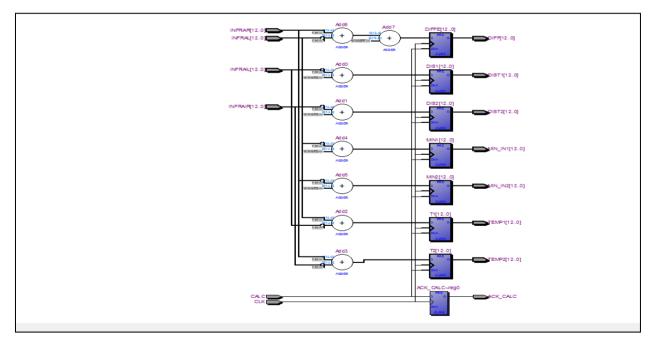

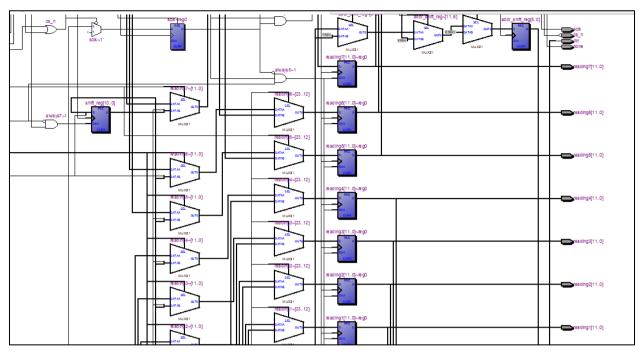

The VHDL block was connected to 2 of the enabling pins on the L293D chip for activating the quadruple high-current half H-Driver chip and for controlling the motor speed. Furthermore, for obtaining the dissimilar directions, the dissimilar outputs generated were used as the input value in the chip. Also the output logic produced by the L293D chip for the disparity movements was described. Figure-7 describes a small portion of the RTL for the calculation block.

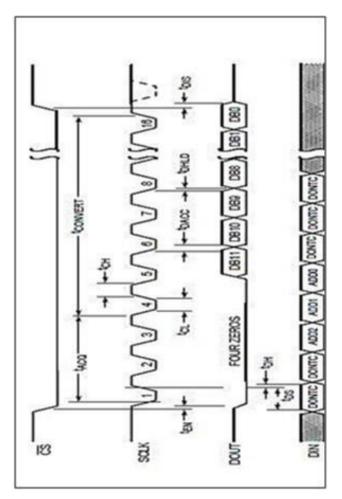

Figure-7. Part of RTL for Calculation block.

The signals obtained from the sensors were transferred using the on-board ADC to the digital signal which could be read by the DE0 board. The ADC type of NS ADC128S022 was used, which used a 12-bit A/D converter input for accessing and interpreting the analogue input value from 0 to 3.3V, which was then rejected by the DE0 Nano board. With regards to the safety problem, it only received and accepted 3.3V. For obtaining an accurate value, the clock frequency assigned to the ADC from 0.8 to 3.2 MHz. Despite these alterations, the ADC worked properly and showed a productivity rate of 50 to 200 ksps, which helped it receive 8 input signals. The control logic and the timing values for the ADC is as per the timing diagram shown in the data sheet (Figure-9).

Figure-9. ADC 128S022 Serial Timing Diagram[6].

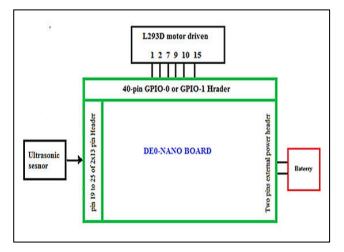

The analogue output was generated with the ultrasonic sensor. The output result was linked from the

pin pairs of 19 to 25 for the pin arrangement of 2x13 Header on the DE0 Nano board. The 19 to 25 pins were 8 input pins for the ADC of the DE0 Nano board. Thereafter, the DE0-Nano controlled the motors using the L293D chip. Furthermore, the pins 2 and 7, 10 and 15, 1 and 9 of the L293D chip were also linked to the one of the 40-pins GPIO header of the DE0 Nano Board. For the efficient working of the DE0 Nano board using the robot platform, 5V had to supply for 2 of the pins in the GPIO header (vcc) or 3.6 - 5.7V to both the pin headers fig 10 describe the ultrasonic sensor connection.

Figure-10. The ultrasonic sensor connection.

#### RESULTS

The Ultrasonic sensor is ideal sensor as they provide stable and accurate readings for a longer distance, consume less power and are inexpensive. This sensor work by estimating the time interval between the signal sent and the subsequent echo generated. This sensor is very useful in low lighting conditions. The US sensor is very effective when the object properties very soft and the object at a larger distance and it's also functional at low levels.

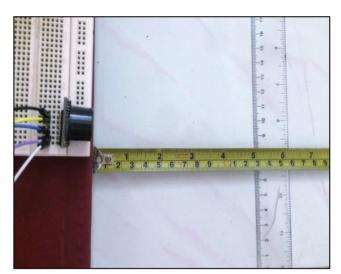

The US sensor had a detection range of 30-500 cm and was basically used for detecting obstacle and avoids it. The US sensor was tested for all the features shown in the data sheet. Noted that, there was a change in the measured beam type when the obstacle of different sizes were placed before the sensor, for example, small obstacle, like a nail. Hence, obstacle varying sizes were used for detecting the accuracy of the US sensors. Obstacle equal to or greater than 11 inches was used, while the small obstacle was approximately 3.5 inch, as described in the data sheet. In Figure-11 shown the US sensor setup.

Figure-11. Setup of the Ultrasonic Sensor.

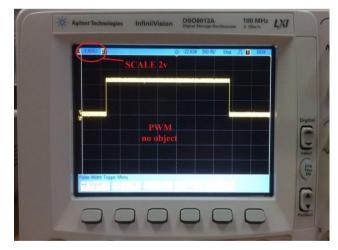

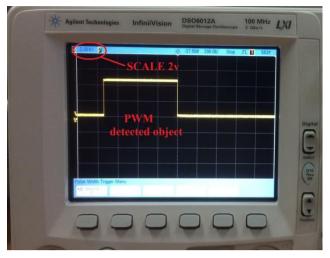

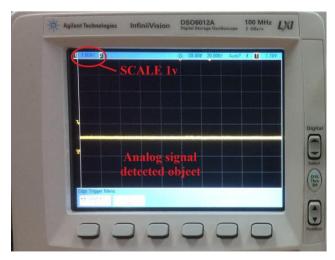

In the first step, the bigger obstaclewas placed in front of the US sensor for determining and quantifying the maximal detection scope of this sensor, as shown in the datasheet. The oscilloscope was used, to estimate the results of the analogue signal and the PWM. It was seen when the obstaclein far point from the US sensor, there was a decrease in the signal detection in oscilloscope display. Similar experiments were carried out using the small obstacleof 3.5 inches. In Figures 12 and 13, were shown the PWM signal results, while Figures 14 and 13 shown the results of the analogue signal.

Figure-12. Oscilloscope display in the absence of an object with a PWM output.

Figure-13. Oscilloscope display in the presence of an object with a PWM output.

Figure-14. Oscilloscope display in the absence of an object with an analogue output.

Figure-15. Oscilloscope display in the presence of an object with an analogue output.

The US sensor was tested using various angles and the testing results were seen it's similar to the radiation beams as shown in Figure-6, and presented in the data sheet.

Here, it was not built a robot, but was designed and implemented an obstacle avoidance system using the FPGA technology. Thus, the default robot system could be controlled by the PIC, hence, the motion and the obstacle detection sensor could also be controlled by the PIC. When the PIC was removed, the robot motion could be directly controlled using the FPGA DE0-Nano Platform. The VHDL code is used with the FPGA for controlling the robot motor. In Table-2, described the robot motion depending on the input values of the Motors A and B and Figure-16 shown the robot doing avoiding.

**Table-2.** The robot Motion based on the input values ofMotors A and B.

| Motion Of The          | Motor A |    | Motor B |    |

|------------------------|---------|----|---------|----|

| Robot                  | RA      | RB | LA      | LB |

| Forward                | 0       | 1  | 0       | 1  |

| Backward               | 1       | 0  | 1       | 0  |

| Left                   | 1       | 0  | 0       | 1  |

| Right                  | 0       | 1  | 1       | 0  |

| Stop                   | 1       | 1  | 1       | 1  |

| Pines of L293D<br>Chip | 2       | 7  | 10      | 15 |

Figure-16. The robot doing avoiding.

(C)

#### www.arpnjournals.com

#### CONCLUSIONS

The project objectives are achieved successfully. VHDL coding was used for design the obstacle avoidance system using the Quartus II 13.0sp1 software, while the design was implemented on the DE0 Nano board, which was the brain of the system. The CAD tool Quartus II 13.0sp1 software acted as the designing tool for simulating the VHDL coding or the block diagram for validating the performance of this design.

Finally, observed that the obstacle avoidance system was flexible enough to be used in any of the platforms, after some modifications. Besides, the ratio of the logic element proved that the DE0 Nano board could implement the complex obstacle avoidance system which is a very encouraging decision for better performance. Furthermore, the FPGA platform could be reconfigured many times, thus providing the designer with many opportunities to change the design without changing the hardware rewiring. Lastly, the frequency of the DE0 Nano Board gave a maximal value of 1.3 GHz, which indicated that the platform's frequency requirement would reach that value and the logic element that have been used in this project is 4, 042. Hence, using the FPGA technology improved the performance of the system.

## ACKNOWLEDGMENT

The authors would like to thank the Ministry of Education Malaysia (MOE) for providing the FRGS research grant (Grant no. 9003-00474).

# REFERENCES

- C. Ababei, S. Duerr, J. Ebel, R. Marineau and M. G. Moghaddam. 2016. Open Source Digital Camera on Field Programmable Gate Arrays. pp. 151-155.

- [2] T. Mohammad. 2009. Using Ultrasonic and Infrared Sensors for Distance Measurement. 3(3): 267-272.

- [3] M. Q. Sedeeq, M. H. Salih, O. F. Yousif and N. Q. Mohammed. 2016. The vantage of utilizing FPGA in the design of an embedded multiprocessor. 11(23): 13815-13827.

- [4] Http://www.terasic.com. No TitleDE0 Nano User Manual. Available: http://www.terasic.com.

- [6] Www.national.com. 2015. ADC128S022 8-Channel, 50 kSPS to 200 kSPS, 12-Bit A / D Converter.