# CONCEPTION AND HARDWARE MINIMIZATION OF A NEW CHIEN SEARCH BLOCK FOR REED SOLOMON CODES WITH IMPLEMENTATION ON FPGA CARD

Mohamed Elghayyaty<sup>1</sup>, Azeddine Wahbi<sup>2</sup>, Anas El Habti El Idrissi<sup>1</sup>, Omar Mouhib<sup>1</sup>, Laamari Hlou<sup>1</sup> and Abdelkader Hadjoudja<sup>1</sup>

<sup>1</sup>Laboratory of Electrical Engineering and Energy System, Faculty of Sciences, University Ibn Tofail Kenitra, Morocco <sup>2</sup>Laboratory of Industrial Engineering, Data Processing and Logistic, Faculty of Sciences Ain Chock, University Hassan II, Casablanca, Morocco

E-Mail: melghayyaty@gmail.com

## ABSTRACT

Error Correcting Codes such as Reed Solomon (RS) and Bose, Chaudhuri, and Hocquenghem (BCH) are widely used in communication and storage systems in order to correct and control errors introduced by transmission channel. In this paper, a simplified algorithm for RS and BCH decoding is proposed with a view to reduce the number of components compared to the basic chien search block. First, we developed the design of the proposed algorithm second, we generated and simulated the hardware description language source code using Quartus software tools and finally we implemented the new algorithm of chien search block on FPGA card.

**Keywords:** error locator polynomial, RS decoder, BCH decoder, chien search block, even polynomial, odd polynomial, FPGA implementation.

# **1. INTRODUCTION**

Error correcting codes are widely used in several fields, such as telecommunications, wireless channels [1] [2] [3]. We also find them in the field of storage. We add to the message to transmit additional information to be able to detect and correct the errors introduced by the transmission channel [4] [5] [6]. As these techniques make it possible to control the errors introduced by the noise of the transmission channel, they are called "channel coding" [7]. The main existing techniques are: RS (Reed-Solomon) codes used in DVB (Digital Video Broadcasting) such as (DVB-T, DVB-S and DVB-C), BCH codes (Bose, Ray-Chaudhuri and Hocquenghem) and Low-Density Parity-Check (LDPC) codes used respectively in DVB-S2 Digital Video Broadcasting - Satellite - Second Generation [8] [9]. In this context, the objective of this work is to present a conception and an optimization of the chien search block compared to the basic one used widely in DVB-S2 [10]. We also prove that it's possible to reduce both the number of components and the response time in the Chien Search Block using the hardware description language VHDL for simulation and Xilinx Spartan 3E-500 FG 320 FPGA (xc3s500e-5fg320) for hardware implementation.

# 2. ERROR LOCATOR POLYNOMIAL

The error locator polynomial E(x) is written to include only the terms that correspond to errors:

$$E(x) = Y_1 X^{e_1} + Y_2 X^{e_2} + \dots + Y_{\nu} X^{e_{\nu}}$$

(1)

Where e1, ... ev, identify the locations of the errors in the code word as the corresponding powers of x, while Y1,...Yv represent the error values at those locations [11].

The error locator polynomial,  $\Lambda$  (x), has a degree of  $\nu \leq t$  and can be represented as:

$$\Lambda(x) = \prod_{i=1}^{\nu} (1 + X_{i}x)$$

(2)

=  $X_{1}(x + X_{1}^{(-1)})X_{2}(x + X_{2}^{(-1)}).$

Where  $X_1 = \alpha^{e_1}$ ,  $X_2 = \alpha^{e_2}$ ... then clearly the function value will be zero if  $x = \alpha^{-e_1}$ ,  $x = \alpha^{-e_2}$ ...

# **3. CHIEN SEARCH ALGORITHM**

This algorithm can detect the error position by calculating  $\Lambda (\alpha^{i})$  where  $0 \le i \le n-1$ , such as  $\Lambda (x)$  is the error locator polynomial calculated with the Euclidean algorithm [12]. For the case of RS (15, 11) we must calculate:  $\Lambda (\alpha^{-14}), \Lambda (\alpha^{-13})... \Lambda (\alpha^{-1}), \Lambda (\alpha^{-0})$

The Table-1 as shown below presents the obtained results:

ISSN 1819-6608

**Table-1.** Roots of error locator polynomial RS (15, 11).

| x                       | x <sup>2</sup> term | x term        | unity | Sum |

|-------------------------|---------------------|---------------|-------|-----|

| α- <sup>14</sup>        | α <sup>13</sup>     | $\alpha^{12}$ | 1     | 3   |

| α- <sup>13</sup>        | $\alpha^0$          | $\alpha^{13}$ | 1     | 13  |

| α- <sup>12</sup>        | $\alpha^2$          | $\alpha^{14}$ | 1     | 12  |

| α- <sup>11</sup>        | $\alpha^4$          | $\alpha^0$    | 1     | 3   |

| α- <sup>10</sup>        | $\alpha^6$          | $\alpha^1$    | 1     | 15  |

| α-9                     | $\alpha^8$          | $\alpha^2$    | 1     | 0   |

| α-8                     | $\alpha^{10}$       | $\alpha^3$    | 1     | 14  |

| α-7                     | $\alpha^{12}$       | $\alpha^4$    | 1     | 13  |

| α-6                     | $\alpha^{14}$       | $\alpha^5$    | 1     | 14  |

| α-5                     | $\alpha^1$          | $\alpha^6$    | 1     | 15  |

| $\alpha$ -4             | $\alpha^3$          | $\alpha^7$    | 1     | 2   |

| α-3                     | $\alpha^5$          | $\alpha^8$    | 1     | 2   |

| $\alpha$ - <sup>2</sup> | α <sup>7</sup>      | α9            | 1     | 0   |

| $\alpha$ - <sup>1</sup> | α9                  | $\alpha^{10}$ | 1     | 12  |

| α-0                     | $\alpha^{11}$       | $\alpha^{11}$ | 1     | 1   |

The two results  $\Lambda$  ( $\alpha^{-14}$ ) and  $\Lambda$  ( $\alpha^{-13}$ ) mean that: the sixth and the thirteenth symbols respectively in the code word contain the errors.

Generally, In the case of RS (n, k), we must calculate:

$$\Lambda$$

( $\alpha^{-(n-1)}$ ),  $\Lambda$  ( $\alpha^{-(n-2)}$ )...  $\Lambda$  ( $\alpha^{-1}$ ),  $\Lambda$  ( $\alpha^{-0}$ )

If the expression reduces to  $0 \Lambda (\alpha^{-i}) = 0$ , then that value of x is a root and identifies the error position else the position does not contain an error.

## **3.1 Proposed Algorithm**

The proposed algorithm is based on a specific and methodic factorization of the error locator polynomial such as  $\{(P (x) = Ax^n + B, where n = 1)\}$  should be depicted in this polynomial. This method allows us to conceive a new circuit of Chien Search Block i.e. we can minimize both the number of components compared to the basic Chien search block [13].

Beginning with the Ttable-2 which describes the Number of minimized logic gates for different error locator polynomials [14].

| Table 2 Number     | of minimized L | logic gotos for | different error | locator polynomials. |

|--------------------|----------------|-----------------|-----------------|----------------------|

| Table-2. INUITIDET |                | logic gales for |                 | iocator porynomials. |

|                    |                |                 |                 |                      |

| Error locator polynomial                                                       | Number of logic<br>gates for the<br>basic circuit | Number of logic<br>gates for the<br>modified circuit | Number of<br>minimized logic<br>gates |

|--------------------------------------------------------------------------------|---------------------------------------------------|------------------------------------------------------|---------------------------------------|

| $\Lambda(X) = AX^2 + BX + C$                                                   | 11                                                | 7                                                    | 4                                     |

| $\Lambda(X) = AX^3 + BX^2 + CX + D$                                            | 15                                                | 9                                                    | 6                                     |

| $\Lambda(X) = AX^4 + BX^3 + CX^2 + DX + E$                                     | 19                                                | 11                                                   | 8                                     |

| · · · · · · · · · · · · · · · · · · ·                                          |                                                   |                                                      |                                       |

| $ \begin{array}{c} \Lambda(X) = A_n X^n + \\ \dots + A_1 X + A_0 \end{array} $ | 3+4n                                              | 3+2n                                                 | 2n                                    |

If we take the polynomial of degree 3 we have:

$$\Lambda(X) = AX^{3} + BX^{2} + CX + D \quad (3)$$

=  $X^{2} (Ax + B) + (Cx + D)$

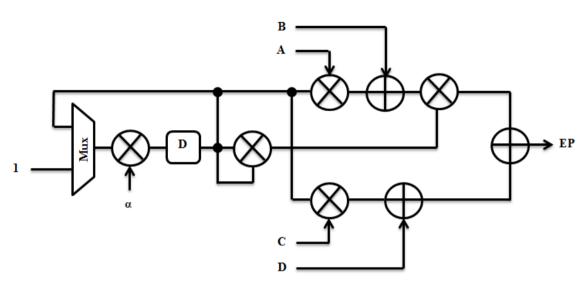

The logic circuit of equation 1 is represented in Figure-1. Also, the Number of logic gates for the basic and modified circuits is represented in Tables-3, 4, 5, 6 and Table-7.

Ø.

www.arpnjournals.com

Figure-1. Modified circuit 2 of Chien Search Block for error locator polynomial as degree 3.

Table-3. Number of logic gates for the basic and modified circuits (polynomial as degree 3).

| Error locator polynomial            | basic circuit | modified circuit 1 | modified circuit 2 |

|-------------------------------------|---------------|--------------------|--------------------|

| $\Lambda(X) = AX^3 + BX^2 + CX + D$ | 15            | 9                  | 10                 |

Table-4. Number of logic gates for the basic and modified circuits (polynomial as degree 4).

| Error locator polynomial                   | basic circuit | modified circuit 1 | modified circuit 2 |

|--------------------------------------------|---------------|--------------------|--------------------|

| $\Lambda(X) = AX^4 + BX^3 + CX^2 + DX + E$ | 19            | 11                 | 13                 |

Table-5. Number of logic gates for the basic and modified circuits (polynomial as degree 5).

| Error locator polynomial                                  | basic circuit | modified circuit 1 | modified circuit 2 |

|-----------------------------------------------------------|---------------|--------------------|--------------------|

| $\Lambda(X) = AX^{5} + BX^{4} + CX^{3} + DX^{2} + EX + F$ | 23            | 13                 | 15                 |

Table-6. Number of logic gates for the basic and modified circuits (polynomial as degree 6).

| Error locator polynomial                                  | basic circuit | modified circuit 1 | modified circuit 2 |

|-----------------------------------------------------------|---------------|--------------------|--------------------|

| $\Lambda(X) = AX^{6}$ $+BX^{5}+CX^{4}+DX^{3}+EX^{2}+FX+G$ | 27            | 15                 | 18                 |

Table-7. Number of logic gates for the basic and modified circuits (polynomial as degree 7).

| Error locator polynomial                                                                                                     | basic circuit | modified circuit 1 | modified circuit 2 |

|------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------|--------------------|

| $\Lambda(X) =$<br>AX <sup>7</sup> +BX <sup>6</sup> +CX <sup>5</sup> +DX <sup>4</sup> +EX <sup>3</sup> +FX <sup>2</sup> +GX+H | 31            | 17                 | 20                 |

If we take the polynomial of degree 8 we have:

$$\Lambda(X) = AX^{8} + BX^{7} + CX^{6} + DX^{5} + EX^{4} + FX^{3} + GX^{2} + HX + I = X^{7} (Ax + B) + X^{5} (Cx + D) + X^{3} (Ex + F) + X (Gx + H) + I \quad (4)$$

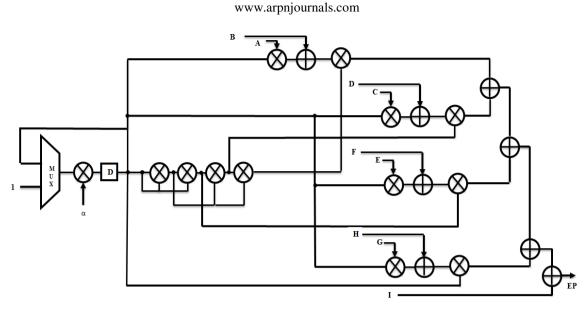

The logic circuit of equation 2 is represented in Figure-2. Also, The Number of logic gates for the basic and modified circuits is represented in Table-8.

Figure-2. Modified circuit 2 of Chien Search Block for error locator polynomial as degree 8.

| Table-8. Number of logic gates for the basic and modified cit | ircuits (polynomial as degree 8). |

|---------------------------------------------------------------|-----------------------------------|

|---------------------------------------------------------------|-----------------------------------|

| Error locator polynomial                                                                                                                      | basic circuit | modified circuit 1 | modified<br>circuit 2 |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------|-----------------------|

| $\Lambda(X) =$<br>AX <sup>8</sup> +BX <sup>7</sup> +CX <sup>6</sup> +DX <sup>5</sup> +EX <sup>4</sup> +FX <sup>3</sup> +GX <sup>2</sup> +HX+I | 35            | 19                 | 23                    |

According to the tables we have adopted previously, we can resume all this in two tables, which show the number of the minimized logic gates using both the basic and the modified circuits for different even and odd error locator polynomials.

| Error locator polynomial                                                                                                                      | basic<br>circuit | modified<br>circuit 1 | modified<br>circuit 2 | Number of<br>minimized<br>logic gates |

|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-----------------------|---------------------------------------|

| $\Lambda(X) = AX^4 + BX^3 + CX^2 + DX + E$                                                                                                    | 19               | 11                    | 13                    | 6                                     |

| $\Lambda(X) = AX^{6} + BX^{5} + CX^{4} + DX^{3} + EX^{2} + FX + G$                                                                            | 27               | 15                    | 18                    | 9                                     |

| $\Lambda(X) =$<br>AX <sup>8</sup> +BX <sup>7</sup> +CX <sup>6</sup> +DX <sup>5</sup> +EX <sup>4</sup> +FX <sup>3</sup> +GX <sup>2</sup> +HX+I | 35               | 19                    | 23                    | 12                                    |

| $\Lambda(X)=A_nX^n$ ++ $A_1X+A_0$                                                                                                             | 3 + 4n           | 3 + 2n                | 3 + n/2 + 2n          | 3n /2                                 |

Table-9. Number of minimized logic gates for different even error locator polynomial.

Table-10. Number of minimized logic gates for different odd error locator polynomial.

| Error locator polynomial                                                                                                     | basic<br>circuit | modified<br>circuit 1 | modified<br>circuit 2 | Number of<br>minimized<br>logic gates |

|------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-----------------------|---------------------------------------|

| $\Lambda(\mathbf{X}) = \mathbf{A}\mathbf{X}^3 + \mathbf{B}\mathbf{X}^2 + \mathbf{C}\mathbf{X} + \mathbf{D}$                  | 15               | 9                     | 10                    | 5                                     |

| $\Lambda(X) = AX^5 + BX^4 + CX^3 + DX^2 + EX + F$                                                                            | 23               | 13                    | 15                    | 8                                     |

| $\Lambda(X) =$<br>AX <sup>7</sup> +BX <sup>6</sup> +CX <sup>5</sup> +DX <sup>4</sup> +EX <sup>3</sup> +FX <sup>2</sup> +GX+H | 31               | 17                    | 20                    | 11                                    |

| $\Lambda(X)=A_nX^n + \dots + A_1X+A_0$                                                                                       | 3 + 4n           | 3 + 2n                | 3 + (5n-1)/2          | 2n – (n -1) /2                        |

# **3.2** Comparison of Circuits

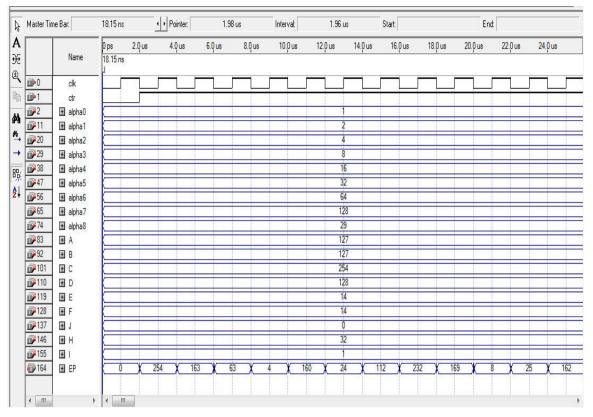

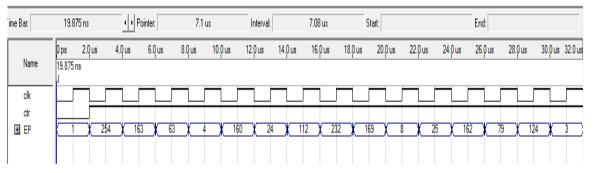

The simulation of the basic and modified circuits is represented respectively in Figures-3 and 4.

Figure-3. Simulation of the basic algorithm for error locator polynomial as degree 8

Figure-4. Simulation of the modified algorithm for error locator polynomial as degree 8.

Commensurate with the simulations and tables we have adopted previously, the results we got in the Figure-4 is the same one in comparison with the basic circuit in Figure-3 but with an important number of minimized logic gates. This minimization can reach 30% compared to the basic algorithms.

# 4. FPGA IMPLEMENTATION

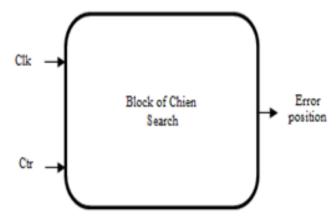

Implementation of a new Chien Search Block for RS and BCH codes has been problematic due to very large amount of resources required we seek to implement a new Chien Search Block on FPGA based on the proposed algorithm to judge the savings in hardware resources [15] [16]. In this paper a parameterized hardware model of the Chien Search Block was developed using the Hardware Description Language (VHDL) and synthesized using Xilinx Synthesis Tool. The block diagram of the proposed algorithm as implemented is shown in Figure-5.

Figure-5. Block diagram of Chien Search block.

The proposed Chien Search Block consists of a global 'Clk' and the error detection process is initiated by

ISSN 1819-6608

#### www.arpnjournals.com

an 'Input', the 'Error position' can be obtained immediately after entering input.

# 4.1 The New Chien Search Block for RS (15, 11) Codes

This algorithm can detect the error position by calculating  $\Lambda$  ( $\alpha^{-i}$ ) where  $0 \le i \le n-1$ , such as  $\Lambda$  (x) is the error locator polynomial, calculated by the Euclidean algorithm. To try the first position in the code word, corresponding to  $e_j = 14$ , we need to substitute  $\alpha^{-14}$  into the locator polynomial:

$$\Lambda(x) = 14x^2 + 14x + 1 \tag{5}$$

Where,

$$\Lambda (\alpha^{-14}) = 14(\alpha^{-14})^2 + 14(\alpha^{-14}) + 1 = 3$$

and the non-zero result shows that the first position does not contain an error. For subsequent position, the power of  $\alpha$  to be substituted will advance by one for the x term and by two for the x<sup>2</sup> term, so we can calculate the calculations as shown in Table-2. The two sum values of zero in Table-2 identify the error positions correctly as the 6th and 13th symbols, corresponding to the x<sup>9</sup> and x<sup>2</sup> terms, respectively, of the code word polynomial.

#### 4.2 Test Procedure for RS (255, 239)

The proposed algorithm was implemented on a Xilinx Spartan 3E-500 FG 320 FPGA (xc3s500e-5fg320). A comprehensive testing environment was developed to test the implemented algorithm. The test setup is shown in Figure-6.

Figure-6.Values of Chien search block for RS (255, 239) codes

The non-zero result in Figure-4 (a) shows that this position does not contain an error. In Figure-9 (b) the value is equal to zero, so this position contains an error.

# 4.3 Comparison of Algorithms

According to the Table-11, which shows the FPGA device utilization summary for RS (255, 239) by using the two algorithms, we can conclude that: The proposed algorithm presents a low complexity and a very good performance compared to the basic algorithm.

| Recources                 | proposed algorithm 1                | proposed algorithm 2 | basic algorithm |

|---------------------------|-------------------------------------|----------------------|-----------------|

| Device                    | Xilinx Spartan 3E (xc3s500e-5fg320) |                      |                 |

| <b>RS</b> (n, k)          | RS (255, 239)                       |                      |                 |

| Number of occupied Slices | 90                                  | 261                  | 119             |

| Number used as Flip Flops | 39                                  | 36                   | 95              |

| Number of 4 input LUTs    | 504                                 | 506                  | 196             |

| Number used as logic      | 504                                 | 481                  | 196             |

Table-11. FPGA device utilization summary for RS (255, 239).

## 5. CONCLUSIONS

A simplified algorithm of Chien Search Block for Reed-Solomon and BCH codes has been presented in this paper. This algorithm is based on a methodic factorization of the error locator polynomial in order to reduce respectively the number of minimized logic gates. The proposed algorithm has been implemented on a Xilinx Spartan 3E-500 FG 320 FPGA (xc3s500e-5fg320). The results show that the proposed algorithm requires reduced hardware resources compared to the basic algorithm.

# REFERENCES

- M. I. Mazurkov, A. V. Sokolov. March 2019. Constructive Synthesis Methods of Binary Error Correcting Code of Length 32 for MC-CDMA Technology. 62(3).

- [2] Zidong Wang, Licheng Wang, Shuai Liu, Guoliang Wei. Jan. 2018. Encoding-Decoding-Based control and filtering of networked systems: insights, developments and opportunities. IEEE/CAA Journal of Automatica Sinica. 5(1).

- [3] K. Deergha Rao. March 2015. Channel Coding Techniques for Wireless Communications, Springer Publishing Company, Incorporated, ISBN: 978-81-322-2291-0.

- [4] K. Manoranjan, M. Chennaiah, K. PrasadBabu, S. Ahmed Basha K. Sudhakar 2017. Implementation of BCH LFSR Encoder Decoder, I Journals: International Journal of Software & Hardware Research in Engineering. 5: 21-30.

- [5] A. El habti, R. El gouri, A. lichioui, H. Laamari. 2015. FPGA implementation of a new BCH decoder used in digital video broadcasting - satellite -second generation (DVB-S2). Journal of Theoretical and Applied Information Technology. 79(1): 22-28.

- [6] Zesong Fei, Jinhong Yuan, and Qin Huang. 2018. Error Control Codes for Next-Generation Communication Systems: Opportunities and Challenges, Wireless Communications and Mobile Computing. Vol. 2018.

- [7] Walled Abdulwhab, Abdulkareem Kadhim Al-Nahrain. September 2018 Comparative Study of Channel Coding Schemes for 5G. Journal of Electronic Systems. 8(3): 95-102.

- [8] M. Shubhangi, B. S. Vaishali. 2019. Implementation of RS-CC Encoder & Decoder using MATLAB. International Journal of Science Technology & Engineering. 5: 22-30.

- [9] Y. Lee, I. Park, Omar Mouhib, Y. Hoyoung. 2018. Area-optimized Syndrome Calculation for Reed-Solomon Decoder. Journal of Semiconductor Technology and Science. 18(5): 610-615.

- [10] Cesar G. Chaves, Eduardo R. de Lima and Jacqueline G. Mertes. 2015. A Synthesizable BCH Decoder for DVB-S2 Satellite Communications. Journal of Integrated Circuits and Systems. 10(3): 174-180.

- [11] M. Elghayyaty, A. Hadjoudja, Omar Mouhib, A. El habti, M. Chakir. 2018. Minimized Logic Gates Number Of Components In The Chien Search Block For Reed-Solomon (RS). American Journal of Engineering Research (AJER). 7(2): 110-116.

- [12] N. Kokubun, A. Yamaga, U. Hironori, D. Watanabe. 2019. Circuit-Size Reduction for Parallel Chien Search using Minimal Polynomial Degree Reduction. IEEE XPLORE.

- [13] S. Roy, A. Mondal, A. El habti, S. S. Garani. 2019. A Fast and Efficient Two-Dimensional Chien Search Algorithm and Design Architecture. IEEE XPLORE. 23(1): 16-19.

- [14] A. El habti, R. El gouri, A. Lichioui and H. Laamari. 2016. Performance study and synthesis of new Error Correcting Codes RS, BCH and LDPC Using the Bit Error Rate (BER) and Field-Programmable Gate Array (FPGA). IJCSNS International Journal of Computer Science and Network Security. 16(5): 21-30.

- [15] Jagannath Samanta, Jaydeb Bhaumik, Soma Barman. March 2017. FPGA based area efficient RS (23, 17) codec, Microsystem Technologies. 23(3).

- [16] J. Athira, B. Yamuna April 2018. FPGA Implementation of an Area Efficient Matrix Code with Encoder Reuse Method. International Conference on Communication and Signal Processing (ICCSP). pp. 0254-0257.